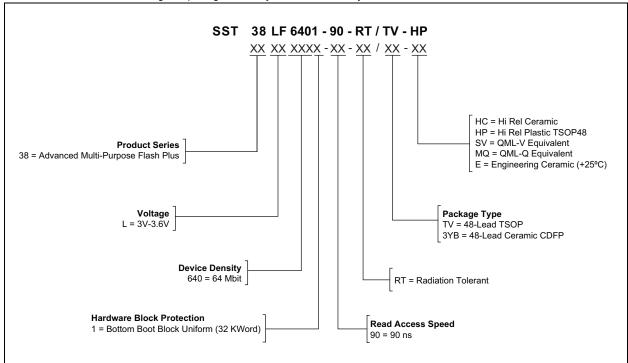

# 64-Mbit (x16) Radiation Tolerant Parallel Flash Memory

#### **Features**

- · Organized as 4M x16

- · Single Voltage Read and Write Operations:

- 3V-3.6V

- Radiation Tolerance Data:

- Total dose:

- Unbiased 75 krad (Si) (Read)/50 krad (Si) (Write)

- Biased 50 krad (Si) (Read)/50 krad (Si) (Write)

- · Heavy Ion Single Event Effects:

- Single Event Upset (SEU) Rate < 5.18 x 10<sup>-22</sup> upsets/bit-day

- Latch-up immunity > 78 MeV.cm<sup>2</sup>/mg (+125°C)

- · Superior Reliability:

- Endurance: 10,000 cycles minimum

- Greater than 20 years data retention

- Low-Power Consumption (typical values at 5 MHz)

- Active current: 4 mA (typical)

- Standby current: 3 µA (typical)

- Auto Low-Power mode: 3 µA (typical)

- 128-Bit Unique ID

- · Security ID Feature:

- 256-word, user One-Time-Programmable (OTP)

- Hardware Reset Pin (RST#)

- Fast Read and Page Read Access Time:

- 90 ns Read access time

- 25 ns Page Read access time

- 4-word Page Read buffer

- · Latched Address and Data

- · Fast Erase Times:

- Sector Erase time: 18 ms (typical)

- Block Erase time: 18 ms (typical)

- Chip Erase time: 40 ms (typical)

- Erase Suspend/Erase Resume Capabilities

- Fast Word and Write Buffer Programming Times:

- Word Program time: 7 μs (typical)

- Write Buffer Programming time: 1.75 μs/word (typical)

- 16-word Write buffer

- · Automatic Write Timing:

- Internal VPP generation

- End-of-Write Detection:

- Toggle bits

- Data# polling

- RY/BY# Output

- CMOS I/O Compatibility

- JEDEC<sup>®</sup> Standard:

- Flash EEPROM pinouts and command sets

- CFI Compliant

- · Temperature Range:

- Military: -55°C to +125°C

- · All Devices are RoHS Compliant

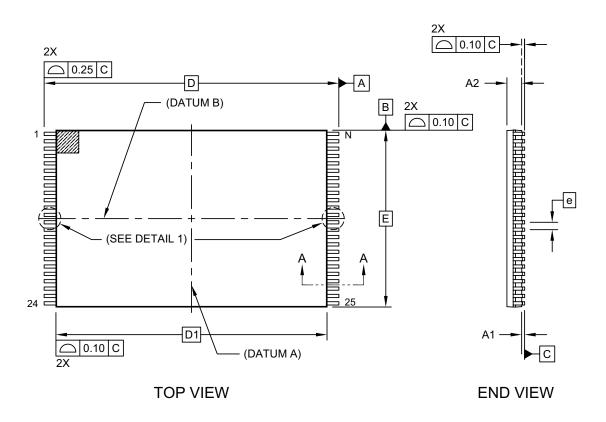

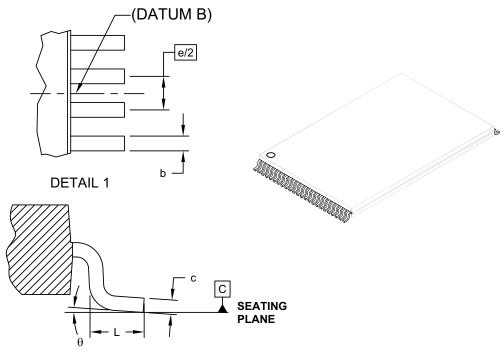

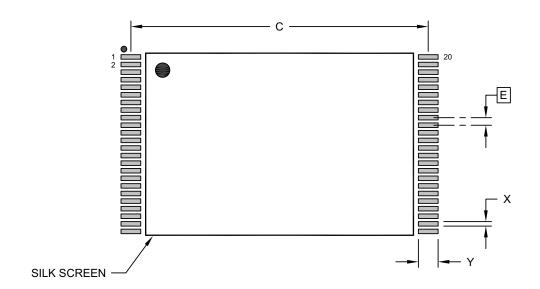

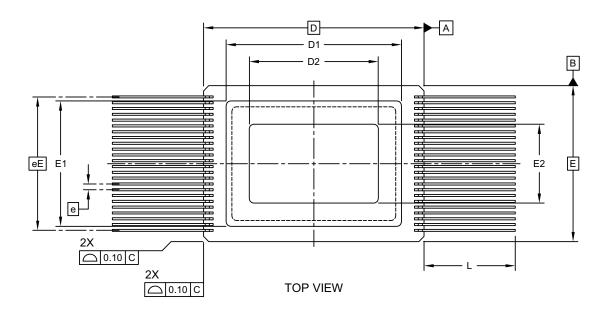

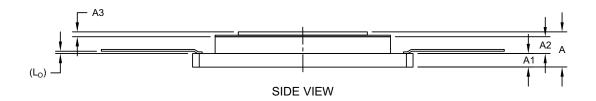

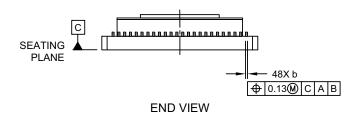

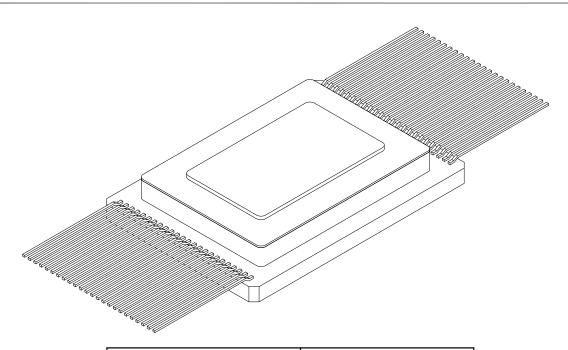

#### **Packages**

- 48-lead TSOP

- · 48-lead Ceramic Dual Flat Package (CDFP)

## **Product Description**

The SST38LF6401RT is a 4M x16 Radiation Tolerant device manufactured with proprietary, high-performance CMOS SuperFlash® technology. The split-gate cell design and thick-oxide tunneling injector attain better reliability and manufacturability compared with alternate approaches. The SST38LF6401RT writes (Program or Erase) with a 3V-3.6V power supply. These devices conform to JEDEC® standard pin assignments for x16 memories.

Featuring high-performance Word Program, the SST38LF6401RT provides a typical Word Program time of 7  $\mu sec.$  For faster word programming performance, the Write Buffer Programming feature has a typical word program time of 1.75  $\mu sec.$  These devices use Toggle Bit or Data# Polling to indicate Program operation completion. In addition to single-word Read, the device also provides a Page Read feature that enables a faster word read time of 25 ns for words on the same page.

The SuperFlash technology provides fixed Erase and Program times, independent of the number of Erase/Program cycles that have occurred.

Therefore, the system software or hardware does not have to be modified or derated as is necessary with alternative Flash technologies, whose Erase and Program times increase with accumulated Erase/Program cycles.

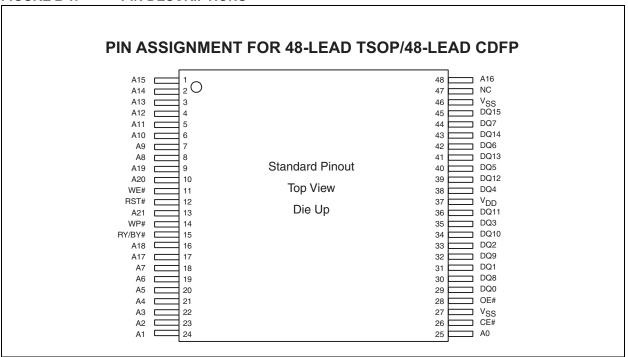

To meet high-density, surface mount requirements, the SST38LF6401RT devices are offered in 48-lead TSOP package and 48-lead Ceramic dual flat package. See Figure 2-1 for pin assignments and Table 2-1 for pin descriptions.

# **Space Quality Grade**

The hermetic SST38LF6401RT is manufactured in compliance with the following MIL class Q or class V requirements: screening testing, qualification testing and TCI/QCI specifications. The plastic SST38LF6401RT is compliant with AEC-Q100 automotive requirements with specific additional tests necessary for space applications. Screening and qualification flows are described in Aerospace and Defense AEQA0242 specification available on Microchip website.

#### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at docerrors@microchip.com. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Website at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Website; http://www.microchip.com

- · Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our website at www.microchip.com to receive the most current information on all of our products.

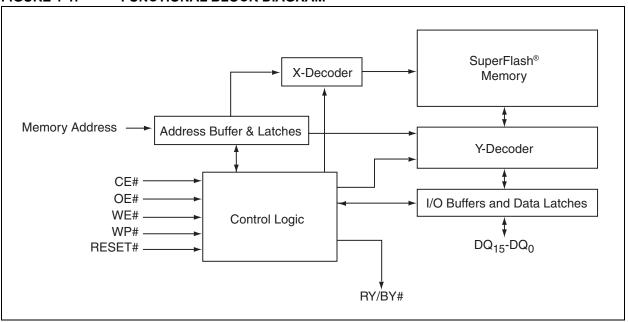

# 1.0 BLOCK DIAGRAM

### FIGURE 1-1: FUNCTIONAL BLOCK DIAGRAM

## 2.0 PIN DESCRIPTION

FIGURE 2-1: PIN DESCRIPTIONS

**TABLE 2-1: PIN DESCRIPTION**

| Symbol                             | Pin Name          | Functions                                                                                                                                                                               |

|------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A <sub>MS</sub> <sup>(1)</sup> -A0 | Address Inputs    | Provide memory addresses.  During Sector Erase A <sub>MS</sub> -A12 address lines will select the sector.  During Block Erase A <sub>MS</sub> -A15 address lines will select the block. |

| DQ15-DQ0                           | Data Input/Output | Output data during Read cycles and receive input data during Write cycles.  Data are internally latched during a Write cycle.  The outputs are in tri-state when OE# or CE# is high.    |

| WP#                                | Write-Protect     | Protect the top/bottom Boot Block from Erase/Program operation when grounded.                                                                                                           |

| RY/BY#                             | Ready/Busy        | Indicate when the device is actively programming or erasing.                                                                                                                            |

| RST#                               | Reset             | Reset and return the device to Read mode.                                                                                                                                               |

| CE#                                | Chip Enable       | Activate the device when CE# is low.                                                                                                                                                    |

| OE#                                | Output Enable     | Gate the data output buffers.                                                                                                                                                           |

| WE#                                | Write Enable      | Control the Write operations.                                                                                                                                                           |

| VDD                                | Power Supply      | Provide power supply voltage: 3V-3.6V                                                                                                                                                   |

| Vss                                | Ground            |                                                                                                                                                                                         |

| NC                                 | No Connection     | Unconnected pins.                                                                                                                                                                       |

Note 1:  $A_{MS}$  = Most significant address  $A_{MS}$  = A21 for SST38LF6401RT

# 3.0 MEMORY MAPS

TABLE 3-1: SST38LF6401RT MEMORY MAP

| SST38LF6401RT          |                        |                               |     |

|------------------------|------------------------|-------------------------------|-----|

| Block <sup>(1,2)</sup> | Sectors <sup>(3)</sup> | Address A21-12 <sup>(4)</sup> | WP  |

| B0 <sup>(5)</sup>      | S0-S7                  | 0000000XXX                    | YES |

| B1                     | S8-S15                 | 0000001XXX                    | NO  |

| B2                     | S16-S23                | 0000010XXX                    | NO  |

| B3                     | S24-S31                | 0000011XXX                    | NO  |

| B4                     | S32-S39                | 0000100XXX                    | NO  |

| B5                     | S40-S47                | 0000101XXX                    | NO  |

| B6                     | S48-S55                | 0000110XXX                    | NO  |

| B7                     | S56-S63                | 0000111XXX                    | NO  |

| B8-B119 follow the s   | ame pattern            |                               |     |

| B120                   | S960-S967              | 1111000XXX                    | NO  |

| B121                   | S968-S975              | 1111001XXX                    | NO  |

| B122                   | S976-S983              | 1111010XXX                    | NO  |

| B123                   | S984-S991              | 1111011XXX                    | NO  |

| B124                   | S992-S999              | 1111100XXX                    | NO  |

| B125                   | S1000-S1007            | 1111101XXX                    | NO  |

| B126                   | S1008-S1015            | 1111110XXX                    | NO  |

| B127                   | S1016-S1023            | 1111111XXX                    | NO  |

Note 1: Each block, B0-B127 is 32-KWord.

- 2: Each block consists of eight sectors.

- 3: Each sector, S0-S1023 is 4-KWord.

- **4:** X = 0 or 1. Block Address (BA) = A21-A15; Sector Address (SA) = A21-A12.

- 5: Block B0 is the Boot Block.

#### 4.0 DEVICE OPERATION

The memory operation functions of this device are initiated using commands written to the device using standard microprocessor Write sequences. A command is written by asserting WE# low while keeping CE# low. The address bus is latched on the falling edge of WE# or CE#, whichever occurs last. The data bus is latched on the rising edge of WE# or CE#, whichever occurs first.

The SST38LF6401RT also has the Auto Low-Power mode which puts the device in a near-standby mode after data have been accessed with a valid Read operation. This reduces the IDD active read current from typically 4 mA to typically 3  $\mu$ A.

The Auto Low-Power mode reduces the typical IDD active read current to the range of 2 mA/MHz of Read cycle time. The device requires no access time to exit the Auto Low-Power mode after any address transition or control signal transition used to initiate another Read cycle. The device does not enter Auto Low-Power mode after power-up with CE# held steadily low, until the first address transition or CE# is driven high.

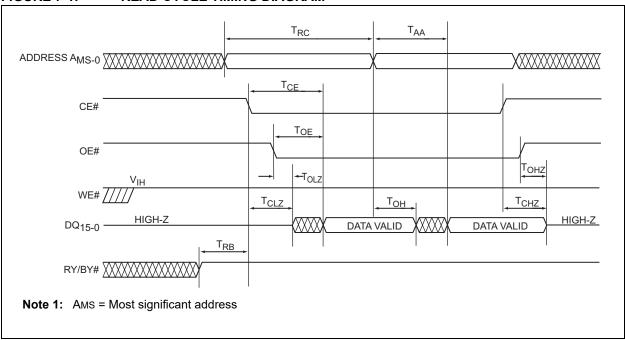

#### 4.1 Read

The Read operation of the SST38LF6401RT is controlled by CE# and OE#, both of which have to be low for the system to obtain data from the outputs. CE# is used for device selection. When CE# is high, the chip is deselected and only standby power is consumed. OE# is the output control and is used to gate data from the output pins. The data bus is in high-impedance state when either CE# or OE# is high. Refer to Figure 7-1 for further details.

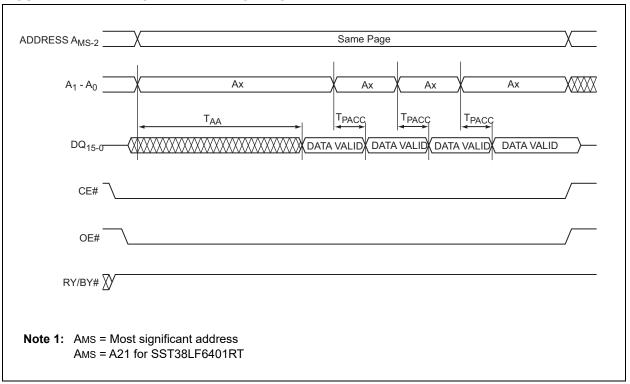

#### 4.2 Page Read

The Page Read operation utilizes an asynchronous method that enables the system to read data from the SST38LF6401RT at a faster rate. This operation allows users to read a four-word page of data at an average speed of 41.25 ns per word.

In Page Read, the initial word read from the page requires TACC to be valid while the remaining three words in the page require only TPACC. All four words in the page have the same address bits, A21-A2, which are used to select the page. Address bits A1 and A0 are toggled, in any order, to read the words within the page.

The Page Read operation of the SST38LF6401RT is controlled by CE# and OE#. Both CE# and OE# must be low for the system to obtain data from the output pins. CE# controls device selection. When CE# is high, the chip is deselected and only standby power is consumed. OE# is the output control and is used to gate data from the output pins. The data bus is in high-impedance state when either CE# or OE# is high. Refer to Figure 7-2 for further details.

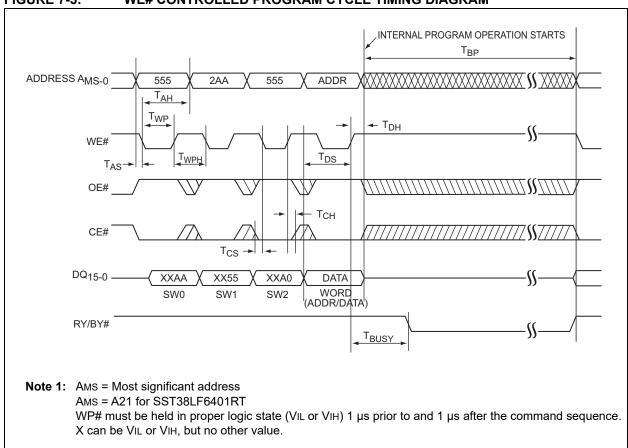

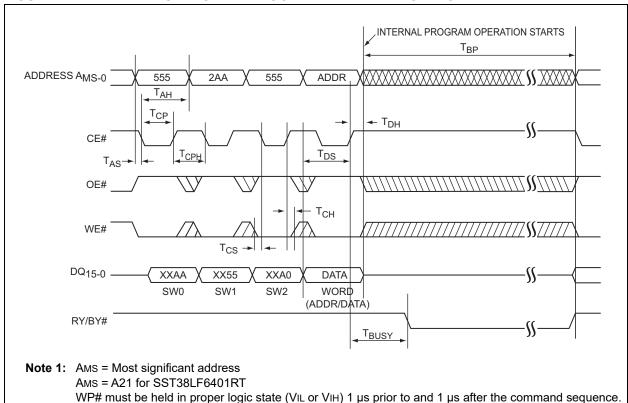

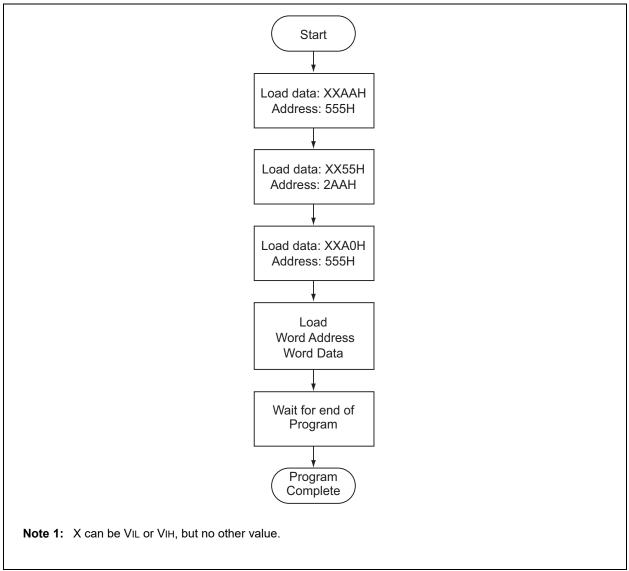

#### 4.3 Word Program Operation

The SST38LF6401RT can be programmed on a word-by-word basis. Before programming, the sector where the word exists must be fully erased. The Program operation is accomplished in three steps.

- 1. The first step is the three-byte load sequence.

- The second step is to load word address and word data. During the Word Program operation, the addresses are latched on the falling edge of either CE# or WE#, whichever occurs last. The data are latched on the rising edge of either CE# or WE#, whichever occurs first.

- 3. The third step is the internal Program operation, which is initiated after the rising edge of the fourth WE# or CE#, whichever occurs first. The Program operation, once initiated, will be completed within 10 µs. See Figures 7-3 and 7-4 for WE# and CE# controlled Program operation timing diagrams and Figure 7-20 for flowcharts.

During the Program operation, the only valid reads are Data# Polling, Toggle Bits and RY/BY#. During the internal Program operation, the host is free to perform additional tasks. Any commands issued during the internal Program operation are ignored. During the command sequence, WP# should be statically held high or low.

When programming more than a few words, Microchip recommends Write-Buffer Programming.

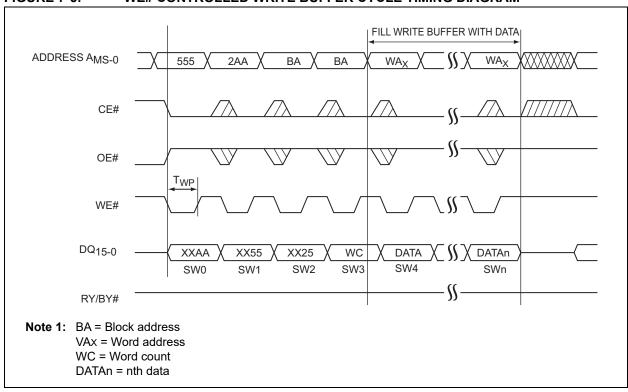

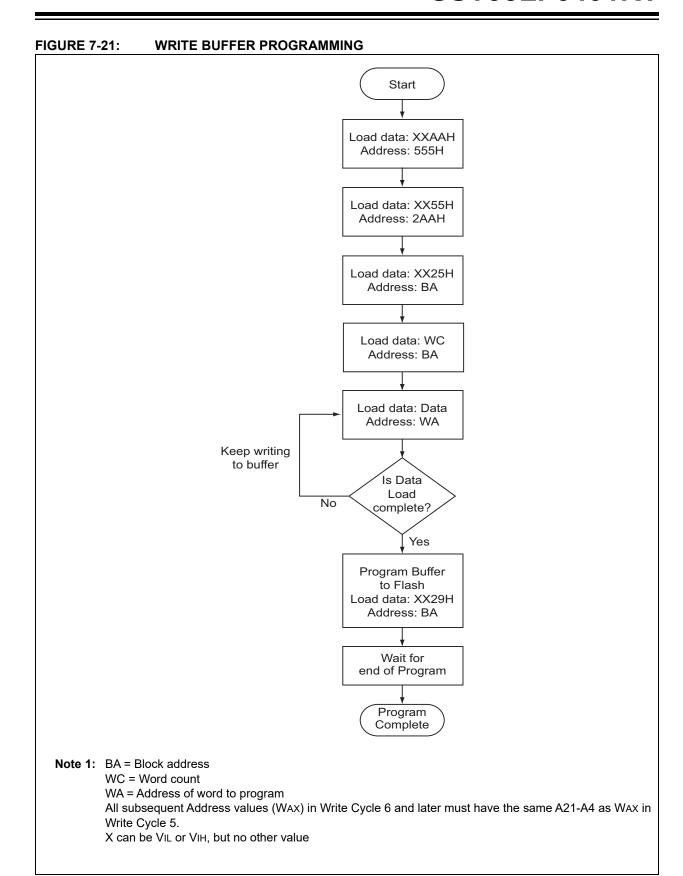

### 4.4 Write Buffer Programming

The SST38LF6401RT offers Write Buffer Programming, a feature that enables faster and more effective word programming. To use this feature, write up to 16 words with the Write-to-Buffer command, then use the Program Buffer-to-Flash command to program the Write Buffer to memory.

The Write-to-Buffer command consists of between 5 and 20 write cycles. The total number of write cycles in the Write-to-Buffer command sequence is equal to the number of words to be written to the buffer plus four.

The first three cycles in the command sequence tell the device that a Write-to-Buffer operation will begin.

The fourth cycle tells the device the number of words to be written into the buffer and the block address of these words. Specifically, the write cycle consists of a block address and a data value called the Word Count (WC), which is the number of words to be written to the buffer minus one. If the WC is greater than 15 (the maximum buffer size minus one), then the operation aborts.

For the fifth cycle and all subsequent cycles of the Write-to-Buffer command, the command sequence consists of the addresses and data of the words to be written into the buffer. All of these cycles must have the same A21-A4 address, otherwise the operation aborts. The number of Write cycles required is equal to the number of words to be written into the Write Buffer, which is equal to WC plus one. The correct number of Write cycles must be issued or the operation will abort. Each Write cycle decrements the Write Buffer counter, even if two or more of the Write cycles have identical address values. Only the final data loaded for each buffer location is held in the Write Buffer.

Once the Write-to-Buffer command sequence is completed, the Program Buffer-to-Flash command should be issued to program the Write Buffer contents to the specified block in memory.

The block address (i.e. A21-A15) in this command must match the block address in the fourth write cycle of the Write-to-Buffer command or the operation aborts. See Table 5-2 for details on Write-to-Buffer and Program Buffer-to-Flash commands.

While issuing these command sequences, the Write Buffer Programming Abort detection bit (DQ1) indicates if the operation has aborted. There are several cases in which the device can abort:

- In the fourth write cycle of the Write-to-Buffer command, if the WC is greater than 15, the operation aborts.

- In the fifth and all subsequent cycles of the Write-to-Buffer command, if the address values, (A21-A4) are not identical, the operation aborts.

- If the number of write cycles between the fifth to the last cycle of the Write-to-Buffer command is greater than WC + 1, the operation aborts.

- After completing the Write-to-Buffer command sequence, issuing any command other than the Program Buffer-to-Flash command aborts the operation.

- Loading a block address (i.e., A21-A15) in the Program Buffer-to-Flash command that does not match the block address used in the Write-to-Buffer command aborts the operation.

If the Write-to-Buffer or Program Buffer-to-Flash operation aborts, then DQ1 = 1 and the device enters Write-Buffer-Abort mode. To execute another operation, a Write-to-Buffer Abort Reset command must be issued to clear DQ1 and return the device to standard read mode.

After the Write-to-Buffer and Program Buffer-to-Flash commands are successfully issued, the programming operation can be monitored using Data# Polling, Toggle Bits and RY/BY#.

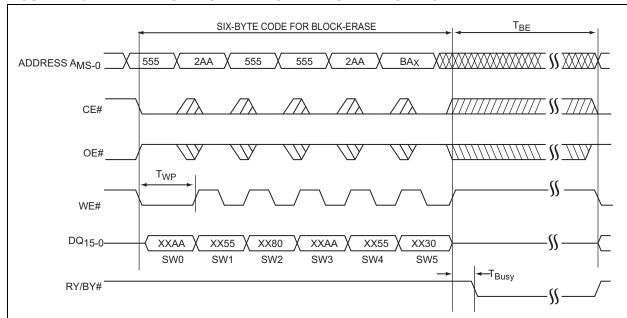

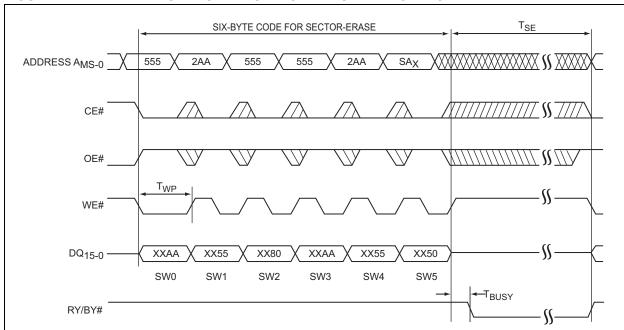

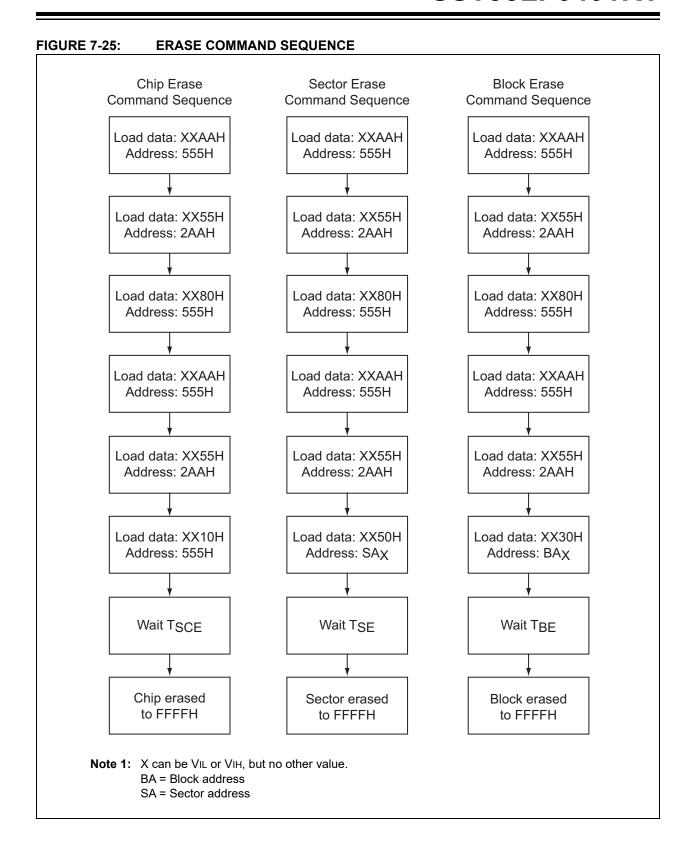

#### 4.5 Sector/Block Erase Operations

The Sector Erase and Block Erase operations allow the system to erase the device on a sector-by-sector or block-by-block basis. The SST38LF6401RT offers both Sector Erase and Block Erase modes.

The Sector Erase architecture is based on a sector size of 4 KWords. The Sector Erase command can erase any 4-KWord sector (S0-S1023).

The Block Erase architecture is based on block size of 32 KWords. In SST38LF6401RT device, the Block Erase command can erase any 32-KWord Block (B0-B127).

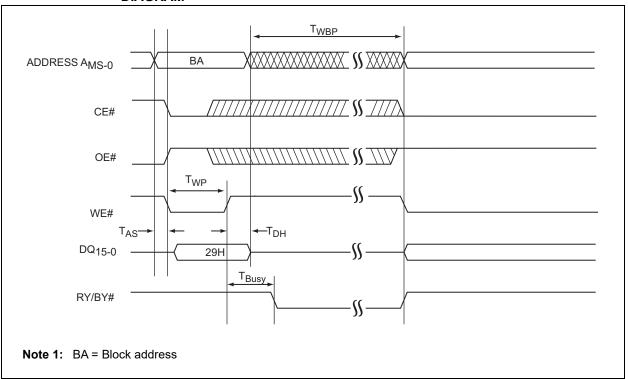

The Sector Erase operation is initiated by executing a six-byte command sequence with Sector Erase command (50H) and sector address (SA) in the last bus cycle. The Block Erase operation is initiated by executing a six-byte command sequence with Block Erase command (30H) and block address (BA) in the last bus cycle. The sector or block address is latched on the falling edge of the sixth WE# pulse, while the command (50H or 30H) is latched on the rising edge of the sixth WE# pulse. The internal Erase operation begins after the sixth WE# pulse. The End-of-Erase operation can be determined using either Data# Polling or Toggle Bit methods. The RY/BY# pin can also be used to monitor the erase operation. For more information, see Figures 7-10 and 7-11 for timing waveforms and Figure 7-25 for the flowchart.

Any commands, other than Erase Suspend, issued during the Sector or Block Erase operation are ignored. Any attempt to Sector or Block Erase memory inside a block protected by Volatile Block Protection, Nonvolatile Block Protection or WP# (low) will be ignored. During the command sequence, WP# should be statically held high or low.

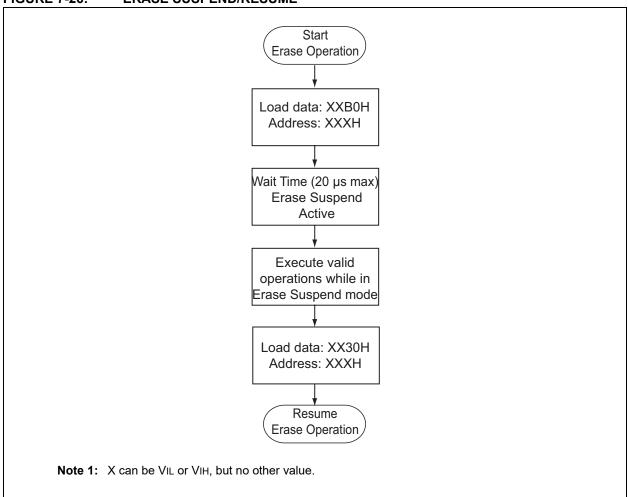

# 4.6 Erase Suspend/Erase Resume Commands

The Erase Suspend operation temporarily suspends a Sector or Block Erase operation, thus allowing data to be read or programmed into any sector or block that is not engaged in an Erase operation. The operation is executed with a one-byte command sequence with Erase Suspend command (B0H). The device automatically enters read mode within 20 µs (maximum) after the Erase Suspend command is issued. Valid data can be read, using a Read or Page Read operation, from any sector or block that is not being erased. Reading at an address location within Erase Suspended sectors or blocks will output DQ2 toggling and DQ6 at '1'. While in Erase Suspend, a Word Program or Write Buffer Programming operation is allowed anywhere except the sector or block selected for Erase Suspend.

To resume a suspended Sector Erase or Block Erase operation, the system must issue the Erase Resume command. The operation is executed by issuing one byte command sequence with Erase Resume command (30H) at any address in the last Byte sequence.

When an erase operation is suspended or re-suspended, after Erase Resume the cumulative time needed for the erase operation to complete is greater than the erase time of a non-suspended erase operation. If the hold time from Erase Resume to the next Erase Suspend operation is less than 200 µs, the accumulative erase time can become very long. Therefore, after issuing an Erase Resume command, the system must wait at least 200 µs before issuing another Erase Suspend command. The Erase Resume command will be ignored until any program operations initiated during Erase Suspend are complete.

Bypass mode can be entered while in Erase Suspend, but only Bypass Word Program is available for those sectors or blocks that are not suspended. Bypass Sector Erase, Bypass Block Erase and Bypass Chip Erase, Erase Suspend and Erase Resume are not available. In order to resume an Erase operation, the Bypass mode must be exited before issuing Erase Resume. For more information about Bypass mode, see Section 4.12 "Bypass Mode".

### 4.7 Chip Erase Operation

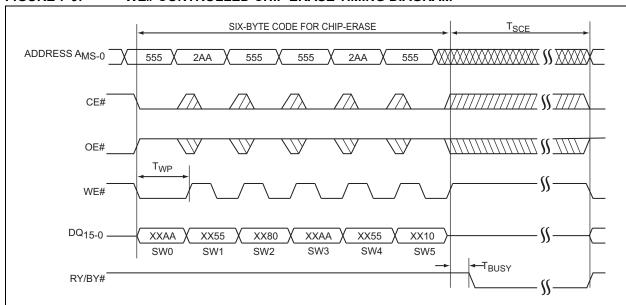

The SST38LF6401RT devices provide a Chip Erase operation that erases the entire memory array to the '1' state. This operation is useful when the entire device must be quickly erased.

The Chip Erase operation is initiated by executing a six-byte command sequence with Chip Erase command (10H) at address 555H in the last byte sequence. The Erase operation begins with the rising edge of the sixth WE# or CE#, whichever occurs first.

During the Erase operation, the only valid reads are Toggle Bit, Data# Polling or RY/BY#. See Table 5-2 for the command sequence, Figure 7-9 for timing diagram and Figure 7-26 for the flowchart. Any commands issued during the Chip Erase operation are ignored. If WP# is low or any VPBs or NVPBs are in the protect state, any attempt to execute a Chip Erase operation is ignored. During the command sequence, WP# should be statically held high or low.

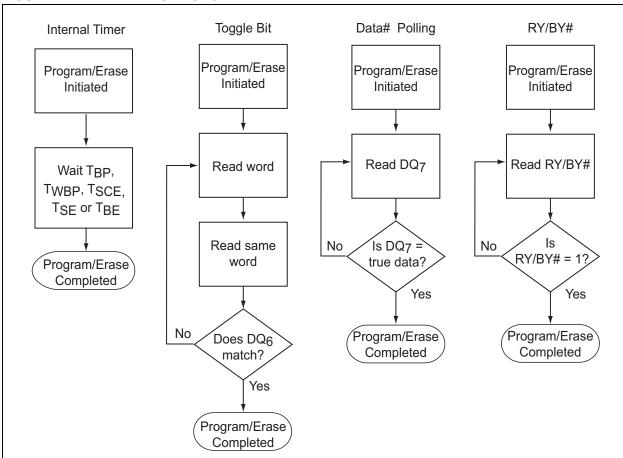

#### 4.8 Write Operation Status Detection

To optimize the system Write cycle time, the SST38LF6401RT provides two software means to detect the completion of a Write (Program or Erase) cycle. The software detection includes two status bits: Data# Polling (DQ7) and Toggle Bit (DQ6). The End-of-Write detection mode is enabled after the rising edge of WE#, which initiates the internal Program or Erase operation.

The actual completion of the nonvolatile write is asynchronous with the system. Therefore, Data# Polling or Toggle Bit maybe be read concurrent with the completion of the write cycle. If this occurs, the system may possibly get an incorrect result from the status detection process. For example, valid data may appear to conflict with either DQ7 or DQ6. To prevent false results upon detection of failures, the software routine should loop to read the accessed location an additional two times. If both reads are valid, then the device has completed the Write cycle; otherwise the failure is valid.

For the Write Buffer Programming feature, DQ1 informs the user if either the Write-to-Buffer or Program Buffer-to-Flash operation aborts. If either operation aborts, then DQ1 = 1. DQ1 must be cleared to '0' by issuing the Write-to-Buffer Abort Reset command.

The SST38LF6401RT also provides an RY/BY# signal. This signal indicates the status of a Program or Erase operation.

If a Program or Erase operation is attempted on a protected sector or block, the operation will abort. After the device initiates an abort, the corresponding Write Operation Status Detection Bits will stay active for approximately 200 ns (program or erase) before the device returns to read mode.

For the status of these bits during a Write operation, see Table 4-1.

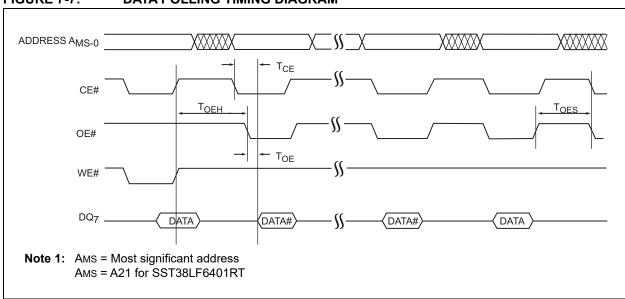

#### 4.8.1 DATA# POLLING (DQ7)

When the SST38LF6401RT is in an internal Program operation, any attempt to read DQ7 will produce the complement of true data. For a Program Buffer-to-Flash operation, DQ7 is the complement of the last word loaded in the Write Buffer using the Write-to-Buffer command. Once the Program operation is completed, DQ7 will produce valid data.

Note that even though DQ7 may have valid data immediately following the completion of an internal Write operation, the remaining data outputs may still be invalid. Valid data on the entire data bus will appear in subsequent successive Read cycles after an interval of 1 µs.

During an internal Erase operation, any attempt to read DQ7 will produce a '0'. Once the internal Erase operation is completed, DQ7 will produce a '1'. The Data# Polling is valid after the rising edge of fourth WE# (or CE#) pulse for Program operation. For Sector, Block or Chip Erase, the Data# Polling is valid after the rising edge of sixth WE# (or CE#) pulse. See Figure 7-7 for Data# Polling timing diagram and Figure 7-22 for a flowchart.

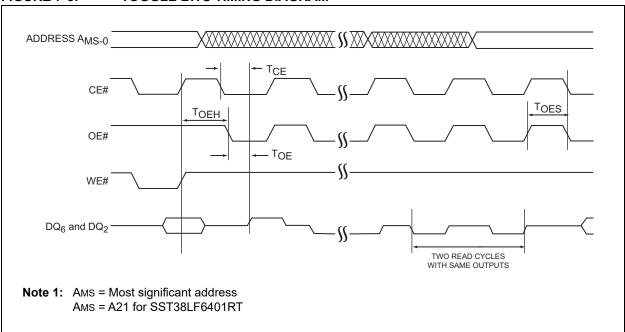

### 4.8.2 TOGGLE BITS (DQ6 AND DQ2)

During the internal Program or Erase operation, any consecutive attempts to read DQ6 will produce alternating '1's and '0's, i.e., toggling between '1' and '0'. When the internal Program or Erase operation is completed, the DQ6 bit will stop toggling and the device is then ready for the next operation. For Sector, Block or Chip Erase, the toggle bit (DQ6) is valid after the rising edge of sixth WE# (or CE#) pulse. DQ6 will be set to '1' if a Read operation is attempted on an Erase Suspended Sector or Block. If Program operation is initiated in a sector/block not selected in Erase Suspend mode, DQ6 will toggle.

An additional Toggle Bit is available on DQ2, which can be used in conjunction with DQ6 to check whether a particular sector or block is being actively erased or erase-suspended. Table 4-1 shows detailed bit status information. The Toggle Bit (DQ2) is valid after the rising edge of the last WE# (or CE#) pulse of Write operation. See Figure 7-8 for Toggle Bit timing diagram and Figure 7-22 for a flowchart.

#### 4.8.3 DQ1

If an operation aborts during a Write-to-Buffer or Program Buffer-to-Flash operation, DQ1 is set to '1'. To reset DQ1 to '0', issue the Write-to-Buffer Abort Reset command to exit the abort state. A power-off/power-on cycle or a Hardware Reset (RST# = 0) will also clear DQ1.

#### 4.8.4 RY/BY#

The RY/BY# pin can be used to determine the status of a Program or Erase operation. The RY/BY# pin is valid after the rising edge of the final WE# pulse in the command sequence. If RY/BY# = 0, then the device is actively programming or erasing. If RY/BY# = 1, the device is in Read mode. The RY/BY# pin is an open drain output pin. This means several RY/BY# can be tied together with a pull-up resistor to VDD.

TABLE 4-1: WRITE OPERATION STATUS

| Status             |                                               | DQ7 <sup>(1)</sup>  | DQ6              | DQ2 <sup>(1)</sup> | DQ1  | RY/BY# <sup>(2)</sup> |

|--------------------|-----------------------------------------------|---------------------|------------------|--------------------|------|-----------------------|

| Normal Operation   | Standard Program                              | DQ7#                | DQ7# Toggle No T |                    | 0    | 0                     |

| Normal Operation   | Standard Erase                                | 0                   | Toggle           | Toggle             | N/A  | 0                     |

|                    | Read from Erase Suspended Sector/Block        | 1                   | No Toggle        | Toggle             | N/A  | 1                     |

| Erase Suspend Mode | Read from Non-Erase<br>Suspended Sector/Block | Data                | Data             | Data               | Data | 1                     |

|                    | Program                                       | DQ7#                | Toggle           | N/A                | N/A  | 0                     |

| Program            | Busy                                          | DQ7# <sup>(3)</sup> | Toggle           | N/A                | 0    | 0                     |

| Buffer-to-Flash    | Abort                                         | DQ7# <sup>(3)</sup> | Toggle           | N/A                | 1    | 0                     |

- Note 1: DQ7 and DQ2 require a valid address when reading status information.

- 2: RY/BY# is an open-drain pin. RY/BY# is high in Read mode and Read in Erase Suspend mode.

- 3: During a Program Buffer-to-Flash operation, the datum on the DQ7 pin is the complement of DQ7 of the last word loaded in the Write Buffer using the Write-to-Buffer command.

#### 4.9 Data Protection

#### 4.9.1 HARDWARE BLOCK PROTECTION

The SST38LF6401RT device supports bottom hardware block protection, which protects the bottom Boot Block of the device. For SST38LF6401RT, the Boot Block consists of the bottom 32-KWord block. The Boot Block addresses are described in Table 4-2.

TABLE 4-2: BOOT BLOCK ADDRESS RANGES

| Product       | Size  | Address Range   |

|---------------|-------|-----------------|

| SST38LF6401RT | 32 kW | 000000H-007FFFH |

Program and Erase operations are prevented on the Boot Block when WP# is low. If WP# is left floating, it is internally held high via a pull-up resistor. When WP# is high, the Boot Block is unprotected, allowing Program and Erase operations on that area.

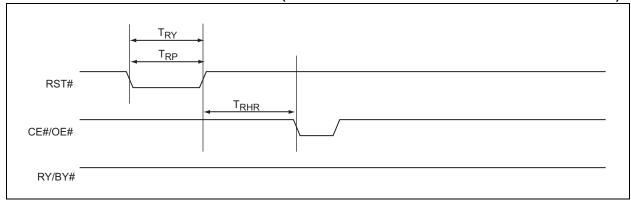

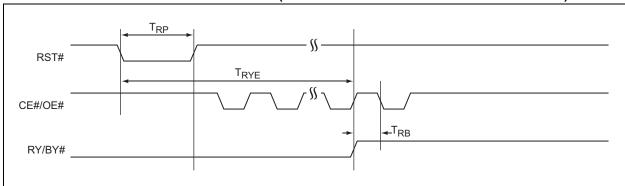

#### 4.9.2 HARDWARE RESET (RST#)

The RST# pin provides a hardware method of resetting the device to read array data. When the RST# pin is held low for at least TRP, any in-progress operation will terminate and return to Read mode. When no internal Program/Erase operation is in progress, a minimum period of TRHR is required after RST# is driven high before a valid Read can take place. See Figure 7-16 for more information.

The interrupted Erase or Program operation must be re-initiated after the device resumes normal operation mode to ensure data integrity.

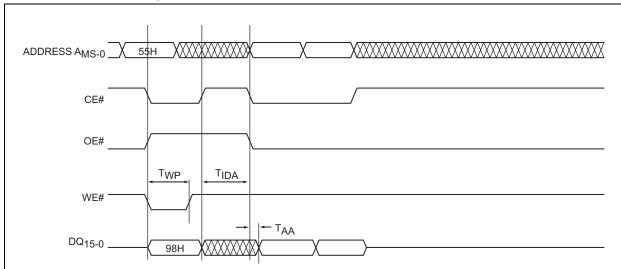

# 4.9.3 COMMON FLASH MEMORY INTERFACE (CFI)

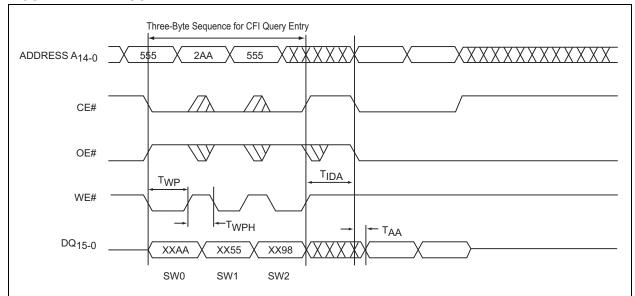

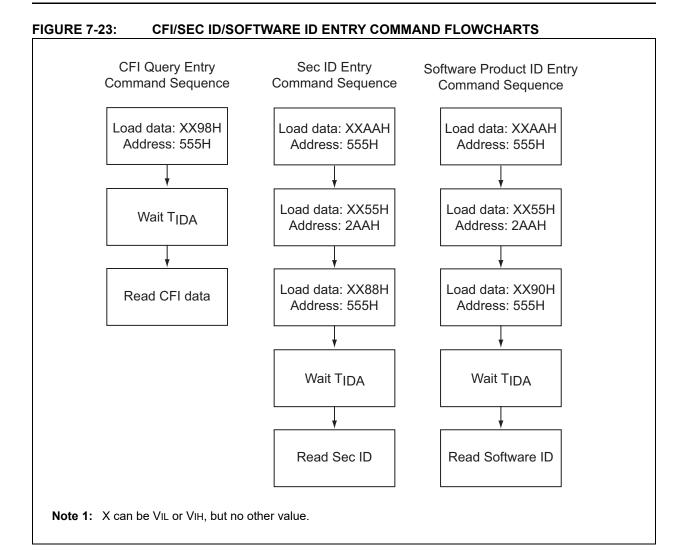

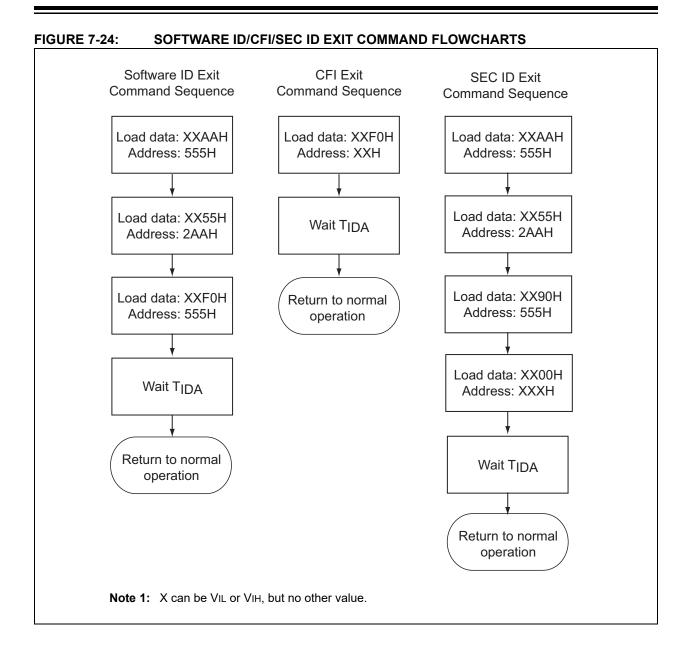

The SST38LF6401RT contains Common Flash Memory Interface (CFI) information that describes the characteristics of the device. In order to enter the CFI Query mode, the system can either write a one-byte sequence using a standard CFI Query Entry command or a three-bye sequence using the SST CFI Query Entry command. A comparison of these two commands is shown in Table 5-2. Once the device enters the CFI Query mode, the system can read CFI data at the addresses given in Table 5-3 through Table 5-5.

The system must write the CFI Exit command to return to Read mode. Note that the CFI Exit command is ignored during an internal Program or Erase operation. See Table 5-2 for software command codes, Figures 7-13 and 7-14 for timing waveform and Figures 7-23 and 7-24 for flowcharts.

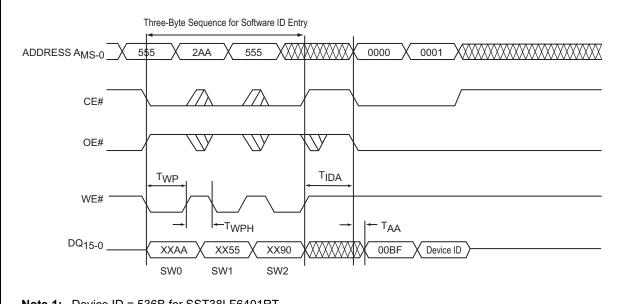

#### 4.10 Product Identification

The Product Identification mode identifies the device as the SST38LF6401RT and the manufacturer as SST. See Table 4-3 for specific address and data information. Product Identification mode is accessed through software operations. The software Product Identification operations identify the part and can be useful when using multiple manufacturers in the same socket. For details, see Table 5-2 for software operation, Figure 7-12 for the software ID Entry and Read timing diagram and Figure 7-23 for the software ID Entry command sequence flowchart.

TABLE 4-3: PRODUCT IDENTIFICATION

|                   | Address | Data |

|-------------------|---------|------|

| Manufacturer's ID | 0000H   | BFH  |

| Device ID         | 0001H   | 536B |

In order to return to the standard Read mode, the software Product Identification mode must be exited. The exit is accomplished by issuing the software ID Exit command sequence, which returns the device to the Read mode.

See Table 5-2 for software command codes, Figure 7-14 for timing waveform and Figures 7-23 and 7-24 for flowcharts.

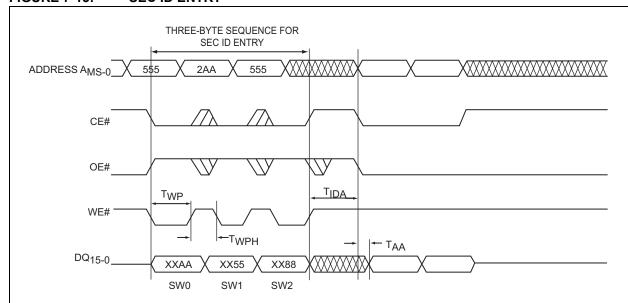

## 4.11 Security ID

The SST38LF6401RT devices offer a Security ID feature. The Secure ID space is divided into two segments:

- · One-factory-programmed 128-bit segment

- · One-user-programmable 256-word segment

See Table 4-4 for address information. The first segment is programmed and locked and contains a 128-bit Unique ID that uniquely identifies the device. The user segment is left unprogrammed for the customer to program as desired.

TABLE 4-4: ADDRESS RANGE FOR SEC ID

|           | Size     | Address   |

|-----------|----------|-----------|

| Unique ID | 128 bits | 000H-007H |

| User      | 256W     | 100H-1FFH |

The user segment of the Security ID can be programmed in several ways. For smaller datasets, use the Security ID Word Program command for word programming. To program larger sets of data more quickly, use the SEC ID Entry command to enter the Secure ID space. Once in the Secure ID space, use the Write Buffer Programming or Bypass Mode feature. Note that the Word Programming command can also be used while in this mode.

To detect end-of-write for the SEC ID, read the toggle bits. Do not use Data# Polling to detect end of Write.

The Secure ID space can be queried by executing a three-byte command sequence with Enter Sec ID command (88H) at address 555H in the last byte sequence. To exit this mode, the Exit Sec ID command should be executed. Refer to Table 5-2 for software commands and Figures 7-23 and 7-24 for flow charts.

#### 4.12 Bypass Mode

Bypass mode shortens the time needed to issue program and erase commands by reducing these commands to two write cycles each. After using the Bypass Entry command to enter the Bypass mode, only the Bypass Word Program, Bypass Sector Erase, Bypass Block Erase, Bypass Chip Erase, Erase Suspend and Erase Resume commands are available. The Bypass Exit command exits Bypass mode. See Table 5-2 for further details.

Entering Bypass Mode while already in Erase Suspend limits the available commands. See Section 4.6 "Erase Suspend/Erase Resume Commands" for more information.

#### 5.0 OPERATIONS

TABLE 5-1: OPERATION MODES SELECTION

| Mode                   | CE# | OE# | WE# | RST# | WP#                    | DQ               | Address                                        |

|------------------------|-----|-----|-----|------|------------------------|------------------|------------------------------------------------|

| Read                   | VIL | VIL | VIH | Н    | Х                      | Dout             | Ain                                            |

| Program                | VIL | ViH | VIL | Н    | VIL/VIH <sup>(1)</sup> | Din              | Ain                                            |

| Erase                  | VIL | VIH | VIL | Н    | VIL/VIH <sup>(1)</sup> | X <sup>(2)</sup> | Sector or block address,<br>XXH for Chip Erase |

| Standby                | VIH | Х   | Х   | VIH  | Х                      | High-Z           | X                                              |

| Write Inhibit          | Х   | VIL | Х   | Х    | Х                      | High-Z/Douт      | X                                              |

| Product Identification | Х   | Х   | VIH | Н    | Х                      | High-Z/Douт      | X                                              |

| Reset                  | Х   | Х   | Х   | L    | Х                      | High-Z           | X                                              |

| Software Mode          | VIL | ViH | VIL | Н    | Х                      | see Table 5-2    | see Table 5-2                                  |

- Note 1: WP# can be VIL when programming or erasing outside of the Boot Block. WP# must be VIH when programming or erasing inside the Boot Block area.

- 2: X can be VIL or VIH, but no other value.

#### TABLE 5-2: SOFTWARE COMMAND SEQUENCE

| Command<br>Sequence    | 1 <sup>st</sup> I<br>Cy | Bus<br>cle        | 2 <sup>nd</sup> Bus<br>Cycle |                   | 3 <sup>rd</sup> Bus Cycle |                   | 4 <sup>th</sup> Bus Cycle |                   | 5 <sup>th</sup> Bus Cycle |                   | 6 <sup>th</sup> Bus Cycle |                   | 7 <sup>th</sup> Bus Cycle |                   |

|------------------------|-------------------------|-------------------|------------------------------|-------------------|---------------------------|-------------------|---------------------------|-------------------|---------------------------|-------------------|---------------------------|-------------------|---------------------------|-------------------|

| Sequence               | Addr <sup>1</sup>       | Data <sup>2</sup> | Addr <sup>1</sup>            | Data <sup>2</sup> | Addr <sup>1</sup>         | Data <sup>2</sup> | Addr <sup>1</sup>         | Data <sup>2</sup> | Addr <sup>1</sup>         | Data <sup>2</sup> | Addr <sup>1</sup>         | Data <sup>2</sup> | Addr <sup>1</sup>         | Data <sup>2</sup> |

| Read <sup>3</sup>      | WA                      | Data              |                              |                   |                           |                   |                           |                   |                           |                   |                           |                   |                           |                   |

| Page Read <sup>3</sup> | WA0                     | Data0             | WA1                          | Data1             | WA2                       | Data2             | WA3                       | Data3             |                           |                   |                           |                   |                           |                   |

| Word<br>Program        | 555H                    | AAH               | 2AAH                         | 55H               | 555H                      | A0H               | WA                        | Data              |                           |                   |                           |                   |                           |                   |

- Note 1: Address format A10-A0 (Hex). Addresses A11- A21 can be VIL or VIH, but no other value, for the SST38LF6401RT command sequence.

- 2: DQ15-DQ8 can be VIL or VIH, but no other value, for command sequence.

- 3: All read commands are in Bold Italics.

- **4:** Total number of cycles in this command sequence depends on the number of words to be written to the buffer. Additional words are written by repeating Write Cycle 5. Address (WA<sub>X</sub>) values for Write Cycle 6 and later must have the same A21-A4 values as WA<sub>X</sub> in Write Cycle 5. WC = Word Count. The value of WC is the number of words to be written into the buffer, minus 1. Maximum WC value is 15 (i.e. F Hex)

- **5**: Erase Suspend and Erase Resume commands are also available in Bypass mode.

- **6:** For SST38LF6401RT, Sector Erase or Block Erase can be used to erase sectors S1016 S1023. Use address SAx. Block Erase cannot be used to erase all 32 kW of Block B127. For SST38LF6401RT, Sector Erase or Block Erase can be used to erase sectors S0-S7. Use address SAx. Block Erase cannot be used to erase all 32 kW of Block B0.

- 7: Once in Sec ID mode, the Word Program, Write Buffer Programming and Bypass Word Program features can be used to program the Sec ID area.

- 8: Unique ID is read with A3 = 0 (Address range = 000000H to 000007H), User portion of Sec ID is read with A8 = 1 (Address range = 000100H to 0001FFH). Lock-out status is read with A7-A0 = FFH. Unlocked: DQ3 = 1/Locked: DQ3 = 0.

- **9:** Both Software ID Exit operations are equivalent.

- **10:** If bits are not locked, then the user-programmable portion of the Sec ID can be programmed over the previously unprogrammed bits (Data = 1) using the Sec ID mode again (bits programmed '0' cannot be reversed to '1'). Valid Word Addresses for the user-programmable portion of the Sec ID are from 000100H-0001FFH.

- 11: The device does not remain in Software Product ID Mode if powered down.

- 12: With Ams-A<sub>1</sub> = 0; Manufacturer ID = 00BFH, is read with A0 = 0, SST38LF6401RT Device ID = 536B, is read with A<sub>0</sub> = 1.

- 13: CFI Query Entry and SST CFI Query Entry are equivalent. Both allow access to the same CFI tables.

TABLE 5-2: SOFTWARE COMMAND SEQUENCE (CONTINUED)

| Command                        | 1 <sup>st</sup> l<br>Cy |                   | 2 <sup>nd</sup><br>Cy |                   | 3 <sup>rd</sup> Bus | s Cycle           | 4 <sup>th</sup> Bus | s Cycle           | 5 <sup>th</sup> Bus | S Cycle           | 6 <sup>th</sup> Bus | s Cycle           | 7 <sup>th</sup> Bus | S Cycle           |

|--------------------------------|-------------------------|-------------------|-----------------------|-------------------|---------------------|-------------------|---------------------|-------------------|---------------------|-------------------|---------------------|-------------------|---------------------|-------------------|

| Sequence                       | Addr <sup>1</sup>       | Data <sup>2</sup> | Addr <sup>1</sup>     | Data <sup>2</sup> | Addr <sup>1</sup>   | Data <sup>2</sup> | Addr <sup>1</sup>   | Data <sup>2</sup> | Addr <sup>1</sup>   | Data <sup>2</sup> | Addr <sup>1</sup>   | Data <sup>2</sup> | Addr <sup>1</sup>   | Data <sup>2</sup> |

| Write Buffer Pro               | gramm                   | ing               |                       |                   |                     |                   |                     |                   |                     |                   |                     |                   |                     |                   |

| Write to Buffer <sup>4</sup>   | 555H                    | AAH               | 2AAH                  | 55H               | ВА                  | 25H               | BA                  | WC                | WA <sub>X</sub>     | Data              | $WA_X$              | Data              | $WA_X$              | Data              |

| Program Buffer<br>to Flash     | BA <sub>X</sub>         | 29H               |                       |                   |                     |                   |                     |                   |                     |                   |                     |                   |                     |                   |

| Write to Buffer<br>Abort Reset | 555H                    | AAH               | 2AAH                  | 55H               | 555H                | F0H               |                     |                   |                     |                   |                     |                   |                     |                   |

| Bypass Mode <sup>5</sup>       |                         |                   |                       |                   |                     |                   |                     |                   |                     |                   |                     |                   |                     |                   |

| Bypass Mode<br>Entry           | 555H                    | AAH               | 2AAH                  | 55H               | 555H                | 20H               |                     |                   |                     |                   |                     |                   |                     |                   |

| Bypass Word<br>Program         | XXXH                    | A0H               |                       | Data              |                     |                   |                     |                   |                     |                   |                     |                   |                     |                   |

| Bypass Sector<br>Erase         | XXXH                    | 80H               |                       | 50H               |                     |                   |                     |                   |                     |                   |                     |                   |                     |                   |

| Bypass Block<br>Erase          | XXXH                    | 80H               |                       | 30H               |                     |                   |                     |                   |                     |                   |                     |                   |                     |                   |

| Bypass Chip<br>Erase           | XXXH                    | 80H               |                       | 10H               |                     |                   |                     |                   |                     |                   |                     |                   |                     |                   |

| Bypass Mode<br>Exit            | XXXH                    | 90H               | 00H                   |                   |                     |                   |                     |                   |                     |                   |                     |                   |                     |                   |

| Erase Related                  |                         |                   |                       |                   |                     |                   |                     |                   |                     |                   |                     |                   |                     |                   |

| Sector Erase                   | 555H                    | AAH               | 2AAH                  | 55H               | 555H                | 80H               | 555H                | AAH               | 2AAH                | 55H               | SA <sub>X</sub>     | 50H               |                     |                   |

| Block Erase <sup>6</sup>       | 555H                    | AAH               | 2AAH                  | 55H               | 555H                | 80H               | 555H                | AAH               | 2AAH                | 55H               | BA <sub>X</sub>     | 30H               |                     |                   |

| Chip Erase                     | 555H                    | AAH               | 2AAH                  | 55H               | 555H                | 80H               | 555H                | AAH               | 2AAH                | 55H               | 555H                | 10H               |                     |                   |

| Erase Suspend                  | XXXH                    | ВОН               |                       |                   |                     |                   |                     |                   |                     |                   |                     |                   |                     |                   |

| Erase Resume                   | XXXH                    | 30H               |                       |                   |                     |                   |                     |                   |                     |                   |                     |                   |                     |                   |

| Security ID                    |                         |                   |                       |                   |                     |                   |                     |                   |                     |                   |                     |                   |                     |                   |

| Sec ID Entry <sup>7</sup>      | 555H                    | AAH               | 2AAH                  | 55H               | 555H                | 88H               |                     |                   |                     |                   |                     |                   |                     |                   |

- Note 1: Address format A10-A0 (Hex). Addresses A11- A21 can be VIL or VIH, but no other value, for the SST38LF6401RT command sequence.

- 2: DQ15-DQ8 can be VIL or VIH, but no other value, for command sequence.

- 3: All read commands are in Bold Italics.

- 4: Total number of cycles in this command sequence depends on the number of words to be written to the buffer. Additional words are written by repeating Write Cycle 5. Address (WA<sub>X</sub>) values for Write Cycle 6 and later must have the same A21-A4 values as WA<sub>X</sub> in Write Cycle 5. WC = Word Count. The value of WC is the number of words to be written into the buffer, minus 1. Maximum WC value is 15 (i.e. F Hex)

- 5: Erase Suspend and Erase Resume commands are also available in Bypass mode.

- **6:** For SST38LF6401RT, Sector Erase or Block Erase can be used to erase sectors S1016 S1023. Use address SAx. Block Erase cannot be used to erase all 32 kW of Block B127. For SST38LF6401RT, Sector Erase or Block Erase can be used to erase sectors S0-S7. Use address SAx. Block Erase cannot be used to erase all 32 kW of Block B0.

- 7: Once in Sec ID mode, the Word Program, Write Buffer Programming and Bypass Word Program features can be used to program the Sec ID area.

- 8: Unique ID is read with A3 = 0 (Address range = 000000H to 000007H), User portion of Sec ID is read with A8 = 1 (Address range = 000100H to 0001FFH). Lock-out status is read with A7-A0 = FFH. Unlocked: DQ3 = 1/Locked: DQ3 = 0.

- **9:** Both Software ID Exit operations are equivalent.

- 10: If bits are not locked, then the user-programmable portion of the Sec ID can be programmed over the previously unprogrammed bits (Data = 1) using the Sec ID mode again (bits programmed '0' cannot be reversed to '1'). Valid Word Addresses for the user-programmable portion of the Sec ID are from 000100H-0001FFH.

- 11: The device does not remain in Software Product ID Mode if powered down.

- 12: With AMS-A<sub>1</sub> = 0; Manufacturer ID = 00BFH, is read with A0 = 0, SST38LF6401RT Device ID = 536B, is read with A<sub>0</sub> = 1.

- 13: CFI Query Entry and SST CFI Query Entry are equivalent. Both allow access to the same CFI tables.

TABLE 5-2: SOFTWARE COMMAND SEQUENCE (CONTINUED)

| Command                                                      | 1 <sup>st</sup> l<br>Cy |                   |                   | Bus<br>cle        | 3 <sup>rd</sup> Bus | s Cycle           | 4 <sup>th</sup> Bu | s Cycle           | 5 <sup>th</sup> Bus | S Cycle           | 6 <sup>th</sup> Bus | s Cycle           | 7 <sup>th</sup> Bus | S Cycle           |

|--------------------------------------------------------------|-------------------------|-------------------|-------------------|-------------------|---------------------|-------------------|--------------------|-------------------|---------------------|-------------------|---------------------|-------------------|---------------------|-------------------|

| Sequence                                                     | Addr <sup>1</sup>       | Data <sup>2</sup> | Addr <sup>1</sup> | Data <sup>2</sup> | Addr <sup>1</sup>   | Data <sup>2</sup> | Addr <sup>1</sup>  | Data <sup>2</sup> | Addr <sup>1</sup>   | Data <sup>2</sup> | Addr <sup>1</sup>   | Data <sup>2</sup> | Addr <sup>1</sup>   | Data <sup>2</sup> |

| Sec ID Read <sup>3,8</sup>                                   | WA <sub>X</sub>         | Data              |                   |                   |                     |                   |                    |                   |                     |                   |                     |                   |                     |                   |

| Sec ID Exit                                                  | 555H                    | AAH               | 2AAH              | 55H               | 555H                | 90H               | XXH                | 00H               |                     |                   |                     |                   |                     |                   |

| Software ID<br>Exit/CFI<br>Exit/Sec ID<br>Exit <sup>9</sup>  | 555H                    | ААН               | 2AAH              | 55H               | 555H                | F0H               |                    |                   |                     |                   |                     |                   |                     |                   |

| Software ID<br>Exit/CFI<br>Exit/Sec ID<br>Exit <sup>10</sup> | XXH                     | F0H               |                   |                   |                     |                   |                    |                   |                     |                   |                     |                   |                     |                   |

| User Security<br>ID Word Pro-<br>gram                        | 555H                    | ААН               | 2AAH              | 55H               | 555H                | A5H               | WA <sub>X</sub>    | Data              |                     |                   |                     |                   |                     |                   |

| User Security<br>ID Program<br>Lock-Out                      | 555H                    | AAH               | 2AAH              | 55H               | 555H                | 85H               | XXH                | 0000H             |                     |                   |                     |                   |                     |                   |

| Product Identific                                            | cation                  |                   |                   |                   |                     |                   |                    |                   |                     |                   |                     |                   |                     |                   |

| Software ID<br>Entry <sup>11</sup>                           | 555H                    | ААН               | 2AAH              | 55H               | 555H                | 90H               |                    |                   |                     |                   |                     |                   |                     |                   |

| Manufacturer<br>ID <sup>3,12</sup>                           | X00                     | BFH               |                   |                   |                     |                   |                    |                   |                     |                   |                     |                   |                     |                   |

| Device ID <sup>3,12</sup>                                    | X01                     | Data              |                   |                   |                     |                   |                    |                   |                     |                   |                     |                   |                     |                   |

| Software ID<br>Exit/CFI<br>Exit/Sec ID<br>Exit <sup>9</sup>  | 555H                    | ААН               | 2AAH              | 55H               | 555H                | F0H               |                    |                   |                     |                   |                     |                   |                     |                   |

| Software ID<br>Exit/CFI<br>Exit/Sec ID<br>Exit <sup>9</sup>  | XXH                     | F0H               |                   |                   |                     |                   |                    |                   |                     |                   |                     |                   |                     |                   |

Note 1: Address format A10-A0 (Hex). Addresses A11- A21 can be VIL or VIH, but no other value, for the SST38LF6401RT command sequence.

- 2: DQ15-DQ8 can be VIL or VIH, but no other value, for command sequence.

- 3: All read commands are in Bold Italics.

- 4: Total number of cycles in this command sequence depends on the number of words to be written to the buffer. Additional words are written by repeating Write Cycle 5. Address (WA<sub>X</sub>) values for Write Cycle 6 and later must have the same A21-A4 values as WA<sub>X</sub> in Write Cycle 5. WC = Word Count. The value of WC is the number of words to be written into the buffer, minus 1. Maximum WC value is 15 (i.e. F Hex)

- 5: Erase Suspend and Erase Resume commands are also available in Bypass mode.

- 6: For SST38LF6401RT, Sector Erase or Block Erase can be used to erase sectors S1016 S1023. Use address SAx. Block Erase cannot be used to erase all 32 kW of Block B127. For SST38LF6401RT, Sector Erase or Block Erase can be used to erase sectors S0-S7. Use address SAx. Block Erase cannot be used to erase all 32 kW of Block B0.

- 7: Once in Sec ID mode, the Word Program, Write Buffer Programming and Bypass Word Program features can be used to program the Sec ID area.

- 8: Unique ID is read with A3 = 0 (Address range = 000000H to 000007H), User portion of Sec ID is read with A8 = 1 (Address range = 000100H to 0001FFH). Lock-out status is read with A7-A0 = FFH. Unlocked: DQ3 = 1/Locked: DQ3 = 0

- 9: Both Software ID Exit operations are equivalent.

- **10:** If bits are not locked, then the user-programmable portion of the Sec ID can be programmed over the previously unprogrammed bits (Data = 1) using the Sec ID mode again (bits programmed '0' cannot be reversed to '1'). Valid Word Addresses for the user-programmable portion of the Sec ID are from 000100H-0001FFH.

- 11: The device does not remain in Software Product ID Mode if powered down.

- 12: With AMS-A<sub>1</sub> = 0; Manufacturer ID = 00BFH, is read with A0 = 0, SST38LF6401RT Device ID = 536B, is read with A<sub>0</sub> = 1.

- 13: CFI Query Entry and SST CFI Query Entry are equivalent. Both allow access to the same CFI tables.

TABLE 5-2: SOFTWARE COMMAND SEQUENCE (CONTINUED)

| Command                                                     | 1 <sup>st</sup> Bus<br>Cycle |                   | 2 <sup>nd</sup> Bus<br>Cycle |                   | 3 <sup>rd</sup> Bus Cycle |                   | 4 <sup>th</sup> Bus Cycle |                   | 5 <sup>th</sup> Bus Cycle |                   | 6 <sup>th</sup> Bus Cycle |                   | 7 <sup>th</sup> Bus Cycle |                   |

|-------------------------------------------------------------|------------------------------|-------------------|------------------------------|-------------------|---------------------------|-------------------|---------------------------|-------------------|---------------------------|-------------------|---------------------------|-------------------|---------------------------|-------------------|

| Sequence                                                    | Addr <sup>1</sup>            | Data <sup>2</sup> | Addr <sup>1</sup>            | Data <sup>2</sup> | Addr <sup>1</sup>         | Data <sup>2</sup> | Addr <sup>1</sup>         | Data <sup>2</sup> | Addr <sup>1</sup>         | Data <sup>2</sup> | Addr <sup>1</sup>         | Data <sup>2</sup> | Addr <sup>1</sup>         | Data <sup>2</sup> |

| CFI                                                         |                              |                   |                              |                   |                           |                   |                           |                   |                           |                   |                           |                   |                           |                   |

| CFI Query<br>Entry <sup>13</sup>                            | 55H                          | 98H               |                              |                   |                           |                   |                           |                   |                           |                   |                           |                   |                           |                   |

| SST CFI Query<br>Entry <sup>13</sup>                        | 555H                         | ААН               | 2AAH                         | 55H               | 555H                      | 98H               |                           |                   |                           |                   |                           |                   |                           |                   |

| Software ID<br>Exit/CFI<br>Exit/Sec ID<br>Exit <sup>9</sup> | 555H                         | ААН               | 2AAH                         | 55H               | 555H                      | F0H               |                           |                   |                           |                   |                           |                   |                           |                   |

| Software ID<br>Exit/CFI<br>Exit/Sec ID<br>Exit <sup>9</sup> | XXH                          | F0H               |                              |                   |                           |                   |                           |                   |                           |                   |                           |                   |                           |                   |

- Note 1: Address format A10-A0 (Hex). Addresses A11- A21 can be VIL or VIH, but no other value, for the SST38LF6401RT command sequence.

- 2: DQ15-DQ8 can be VIL or VIH, but no other value, for command sequence.

- 3: All read commands are in Bold Italics.

- 4: Total number of cycles in this command sequence depends on the number of words to be written to the buffer. Additional words are written by repeating Write Cycle 5. Address (WA<sub>X</sub>) values for Write Cycle 6 and later must have the same A21-A4 values as WA<sub>X</sub> in Write Cycle 5. WC = Word Count. The value of WC is the number of words to be written into the buffer, minus 1. Maximum WC value is 15 (i.e. F Hex)

- 5: Erase Suspend and Erase Resume commands are also available in Bypass mode.

- **6:** For SST38LF6401RT, Sector Erase or Block Erase can be used to erase sectors S1016 S1023. Use address SAx. Block Erase cannot be used to erase all 32 kW of Block B127. For SST38LF6401RT, Sector Erase or Block Erase can be used to erase sectors S0-S7. Use address SAx. Block Erase cannot be used to erase all 32 kW of Block B0.

- 7: Once in Sec ID mode, the Word Program, Write Buffer Programming and Bypass Word Program features can be used to program the Sec ID area.

- 8: Unique ID is read with A3 = 0 (Address range = 000000H to 000007H), User portion of Sec ID is read with A8 = 1 (Address range = 000100H to 0001FFH). Lock-out status is read with A7-A0 = FFH. Unlocked: DQ3 = 1/Locked: DQ3 = 0

- **9:** Both Software ID Exit operations are equivalent.

- 10: If bits are not locked, then the user-programmable portion of the Sec ID can be programmed over the previously unprogrammed bits (Data = 1) using the Sec ID mode again (bits programmed '0' cannot be reversed to '1'). Valid Word Addresses for the user-programmable portion of the Sec ID are from 000100H-0001FFH.

- 11: The device does not remain in Software Product ID Mode if powered down.

- 12: With AMS-A<sub>1</sub> = 0; Manufacturer ID = 00BFH, is read with A0 = 0, SST38LF6401RT Device ID = 536B, is read with A<sub>0</sub> = 1.

- 13: CFI Query Entry and SST CFI Query Entry are equivalent. Both allow access to the same CFI tables.

#### **Note:** Table 5-2 uses the following abbreviations:

- •X = Don't care (VIL or VIH, but no other value)

- •SA<sub>X</sub> = Sector Address; uses AMS-A<sub>12</sub> address lines

- •BA<sub>X</sub>= Block Address; uses A<sub>MS</sub>-A<sub>15</sub> address lines

- •WA = Word Address

- •WC = Word Count

- •PWA<sub>X</sub> = Password Address; PWA<sub>X</sub> = PWA<sub>0</sub>, PWA<sub>1</sub>, PWA<sub>2</sub> or PWA<sub>3</sub>; A1 and A0 are used to select each 16-bit portion of the password

- •PWD<sub>X</sub> = Password Data; PWD<sub>X</sub> = PSWD<sub>0</sub>, PWD<sub>1</sub>, PWD<sub>2</sub> or PWD<sub>3</sub>

- •AMS = Most significant address

TABLE 5-3: CFI QUERY IDENTIFICATION STRING<sup>(1)</sup>

| Address | Data  | Description                                                 |

|---------|-------|-------------------------------------------------------------|

| 10H     | 0051H |                                                             |

| 11H     | 0052H | Query Unique ASCII string "QRY"                             |

| 12H     | 0059H |                                                             |

| 13H     | 0002H | Drimary OEM command act                                     |

| 14H     | 0000H | Primary OEM command set                                     |

| 15H     | 0040H | Address for Primary Extended Table                          |

| 16H     | 0000H | Address for Primary Extended Table                          |

| 17H     | 0000H | Alternate OFM command set (00LL = nane eviste)              |

| 18H     | 0000H | Alternate OEM command set (00H = none exists)               |

| 19H     | 0000H | Address for Alternate OEM Extended Table (00H = none exita) |

| 1AH     | 0000H | Address for Alternate OEM Extended Table (00H = none exits) |

Note 1: Refer to CFI publication 100 for more details.

#### TABLE 5-4: SYSTEM INTERFACE INFORMATION

| Address | Data  | Description                                                                                                               |

|---------|-------|---------------------------------------------------------------------------------------------------------------------------|

| 1BH     | 0030H | VDD Minimum (Program/Erase) DQ7-DQ4: Volts, DQ3-DQ0: 100 millivolts                                                       |

| 1CH     | 0036H | VDD Maximum (Program/Erase) DQ7-DQ4: Volts, DQ3-DQ0: 100 millivolts                                                       |

| 1DH     | 0000H | VPP Minimum (00H = no VPP pin)                                                                                            |

| 1EH     | 0000H | VPP Maximum (00H = no VPP pin)                                                                                            |

| 1FH     | 0003H | Typical time out for Word Program $2^N \mu s$ ( $2^3 = 8 \mu s$ )                                                         |

| 20H     | 0003H | Typical time out for minimum size buffer program 2 <sup>N</sup> μs (00H = not supported)                                  |

| 21H     | 0004H | Typical time out for individual Sector/Block-Erase 2 <sup>N</sup> ms (2 <sup>4</sup> = 16 ms)                             |

| 22H     | 0005H | Typical time out for Chip Erase 2 <sup>N</sup> ms (2 <sup>5</sup> = 32 ms)                                                |

| 23H     | 0001H | Maximum time out for Word Program $2^N$ times typical $(2^1 \times 2^3 = 16 \mu s)$                                       |

| 24H     | 0003H | Maximum time out for buffer program 2 <sup>N</sup> times typical                                                          |

| 25H     | 0001H | Maximum time out for individual Sector/Block-Erase 2 <sup>N</sup> times typical (2 <sup>1</sup> x 2 <sup>4</sup> = 32 ms) |

| 26H     | 0001H | Maximum time out for Chip Erase $2^N$ times typical ( $2^1 \times 2^5 = 64 \text{ ms}$ )                                  |

#### TABLE 5-5: DEVICE GEOMETRY INFORMATION

| Address | Data  | Description                                                                        |

|---------|-------|------------------------------------------------------------------------------------|

| 27H     | 0017H | Device size = 2 <sup>N</sup> Bytes (17H = 23; 2 <sup>23</sup> = 8 Mbyte)           |

| 28H     | 0001H | Flash Device Interface description; 0001H = x16-only asynchronous interface        |

| 29H     | 0000H | Triasif Device interface description, 000 fm – x10-01lly asynchronous interface    |

| 2AH     | 0005H | Maximum number of bytes in multi-byte write = 2 <sup>N</sup> (00H = not supported) |

| 2BH     | 0000H | - Maximum number of bytes in multi-byte write – 2 (00H – not supported)            |

| 2CH     | 0002H | Number of Erase Sector/Block sizes supported by device                             |

| 2DH     | 00FFH | Sector Information (y + 1 = Number of sectors; z x 256B = sector size)             |

| 2EH     | 0003H | y = 2047 + 1 = 2048 sectors (03FFH = 1023)                                         |

| 2FH     | 0000H |                                                                                    |

| 30H     | 0001H | z = 32 x 256 Bytes = 8 Kbytes/sector (0100H = 32)                                  |

# TABLE 5-5: DEVICE GEOMETRY INFORMATION (CONTINUED)

| Address | Data  | Description                                                         |

|---------|-------|---------------------------------------------------------------------|

| 31H     | 007FH | Block Information (y + 1 = Number of blocks; z x 256B = block size) |

| 32H     | 0000H | y =127 + 1 = 128 blocks (007FH = 127)                               |

| 33H     | 0000H |                                                                     |

| 34H     | 0001H | z = 256 x 256 Bytes = 64 Kbytes/block (0100H = 256)                 |

#### 6.0 ELECTRICAL SPECIFICATIONS

# Absolute Maximum Ratings (†)

| Temperature under bias                                    | 55°C to +125°C        |

|-----------------------------------------------------------|-----------------------|

| Storage temperature                                       | 65°C to +150°C        |

| DC voltage on any pin to ground potential                 | 0.5V to VDD+0.5V      |

| Transient voltage (<20 ns) on any pin to ground potential | 2.0V to VDD+2.0V      |

| Surface mount solder reflow temperature                   | +260°C for 10 seconds |

| Output short circuit current <sup>(1)</sup>               | 50 mA                 |

**† NOTICE:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

Note 1: Output shorted for no more than one second. No more than one output shorted at a time.

#### TABLE 6-1: OPERATING RANGE

| Range    | Ambient Temperature | VDD     |  |

|----------|---------------------|---------|--|

| Military | -55°C to +125°C     | 3V-3.6V |  |

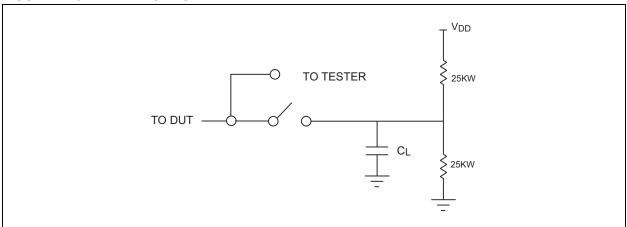

### TABLE 6-2: AC CONDITIONS OF TEST<sup>(1)</sup>

| Input Rise/Fall Time | Output Load |

|----------------------|-------------|

| 5 ns                 | CL = 30 pF  |

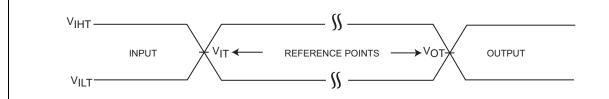

Note 1: See Figures 7-18 and 7-19.

# TABLE 6-3: RECOMMENDED THERMAL OPERATING CONDITION

| Symbol             | Parameter                              | Min. | Тур. | Max.  | Units | Conditions                                                      |

|--------------------|----------------------------------------|------|------|-------|-------|-----------------------------------------------------------------|

| ТА                 | Operating Temperature                  | -55  | _    | 125   | °C    |                                                                 |

| TJ                 | Junction Temperature                   | _    | _    | 134   | °C    | TSOP                                                            |

| TJ                 | Junction Temperature                   | _    | _    | 126.4 | °C    | CDFP                                                            |

| RJA <sup>(1)</sup> | Junction-to-Ambient Thermal Resistance | _    | _    | 50.2  | °C/W  | TSOP                                                            |

| RJA <sup>(1)</sup> | Junction-to-Ambient Thermal Resistance | _    | _    | 7.7   | °C/W  | CDFP                                                            |

| RJC <sup>(2)</sup> | Junction-to-Case Thermal Resistance    | ı    |      | 8.0   | °C/W  | TSOP                                                            |

| RJC <sup>(2)</sup> | Junction-to-Case Thermal Resistance    | l    |      | 3.7   | °C/W  | CDFP                                                            |

| PD                 | Power Dissipation                      |      |      | 0.18  | W     | Vcc = 3.6V, Icc = 50 mA during<br>Program Write Buffer to Flash |

Note 1: Simulated in still air conditions.

2: Simulated in vacuum environment.

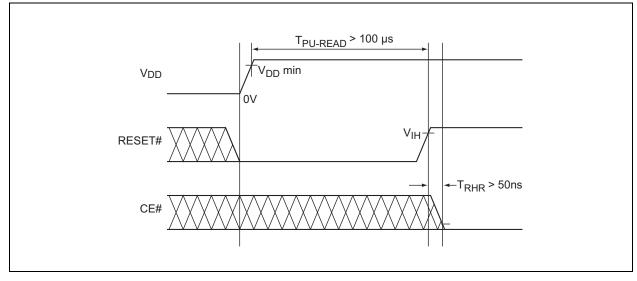

### 6.1 Power-Up Specifications

All functionalities and DC specifications are specified for a VDD ramp rate of greater than 1V per 100 ms (0V to 3.0V in less than 300 ms). If the VDD ramp rate is slower than 1V per 100 ms, a hardware Reset is required. The recommended VDD power-up to RESET# high time should be greater than 100  $\mu s$  to ensure a proper Reset. See Table 6-4 and Figure 6-1 for more information.

TABLE 6-4: RECOMMENDED SYSTEM POWER-UP TIMINGS

| Symbol                   | Parameter                           | Minimum | Units |

|--------------------------|-------------------------------------|---------|-------|

| TPU-READ <sup>(1)</sup>  | Power-Up to Read Operation          | 100     | μs    |

| TPU-WRITE <sup>(1)</sup> | Power-Up to Erase/Program Operation | 100     | μs    |

**Note 1:** This parameter is measured only for initial qualification and after a design or process change that could affect this parameter.

FIGURE 6-1: POWER-UP DIAGRAM

#### 7.0 DC CHARACTERISTICS

TABLE 7-1: DC OPERATING CHARACTERISTICS (VDD = 3.0V-3.6V)<sup>(1)</sup>

|        |                                           | Limits  |      |      |                                                                   |

|--------|-------------------------------------------|---------|------|------|-------------------------------------------------------------------|

| Symbol | Parameter                                 | Min.    | Max. | Unit | Test Conditions                                                   |

|        | Power Supply Current                      | _       | _    |      | Address Input = VILT/VILT <sup>(2)</sup> , VDD = VDD maximum      |

|        | Read <sup>(3)</sup>                       | _       | 18   | mA   | CE# = VIL, OE# = WE# = VIH at f = 5 MHz                           |

| IDD    | Intra-Page Read @5 MHz                    | _       | 2.5  | mA   | CE# = VIL, OE# = WE# = VIH                                        |

| טטו    | Intra-Page Read @40 MHz                   | _       | 20   | mA   | CE# = VIL, OE# = WE# = VIH                                        |

|        | Program and Erase                         | _       | 35   | mA   | CE# = WE# = VIL, OE# = VIH                                        |

|        | Program Write Buffer-to-Flash             | _       | 50   | mA   | CE# = WE# = VIL, OE# = VIH                                        |

| ISB    | Standby Current VDD                       | _       | 60   | μΑ   | CE# = Vih, Vdd = Vdd maximum                                      |

| IALP   | Auto Low Power                            | _       | 60   | μΑ   | CE# = VILC, VDD = VDD maximum All inputs = Vss or VDD, WE# = VIHC |

| ILI    | Input Leakage Current                     | _       | 1    | μΑ   | VIN = GND to VDD, VDD = VDD maximum                               |

| ILIW   | Input Leakage Current on WP# Pin and RST# | _       | 10   | μΑ   | WP# = GND to VDD or RST# = GND to VDD                             |

| ILO    | Output Leakage Current                    | _       | 10   | μΑ   | VOUT = GND to VDD, VDD = VDD maximum                              |

| VIL    | Input Low Voltage                         | _       | 8.0  | V    | VDD = VDD minimum                                                 |

| VILC   | Input Low Voltage (CMOS)                  | _       | 0.3  | V    | VDD = VDD maximum                                                 |

| VIH    | Input High Voltage                        | 0.7Vdd  | _    | V    | VDD = VDD maximum                                                 |

| VIHC   | Input High Voltage (CMOS)                 | VDD-0.3 | _    | V    | VDD = VDD maximum                                                 |

| Vol    | Output Low Voltage                        | _       | 0.2  | V    | IOL = 100 μA, VDD = VDD minimum                                   |

| Vон    | Output High Voltage                       | VDD-0.2 | _    | V    | IOH = 100 μA, VDD = VDD minimum                                   |

**Note 1:** Typical conditions for the Active Current shown on the front page of the data sheet are average values at +25°C (room temperature) and VDD = 3V. Not 100% tested.

TABLE 7-2: CAPACITANCE (TA = 25°C, F = 1 MHZ, OTHER PINS OPEN)

| Parameter           | Description         | Test Condition | Maximum |

|---------------------|---------------------|----------------|---------|

| Cı/o <sup>(1)</sup> | I/O Pin Capacitance | VI/O = 0V      | 12 pF   |

| CIN <sup>(1)</sup>  | Input Capacitance   | VIN = 0V       | 6 pF    |