# AT84AS003 10-bit 1.5 Gsps ADC With 1:4 DMUX

# **Datasheet**

#### **Features**

- 10-bit Resolution

- 1.5 Gsps Sampling Rate

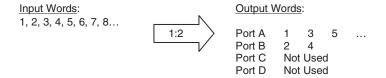

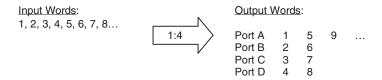

- Selectable 1:2 or 1:4 Demultiplexed Output

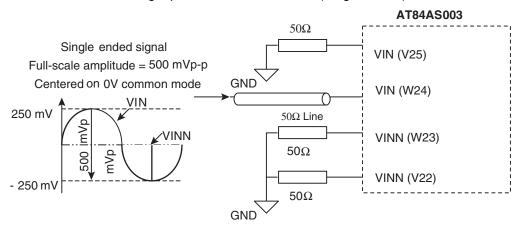

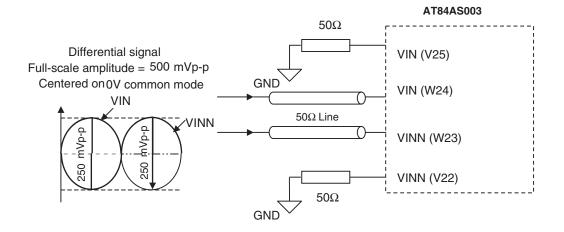

- 500 mVpp Differential 100 $\Omega$  or Single-ended 50 $\Omega$  Analog Input

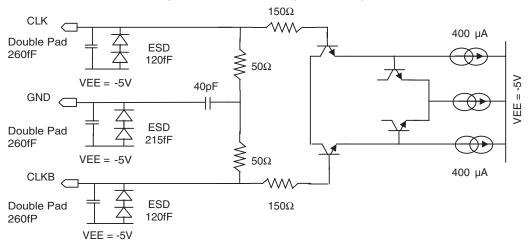

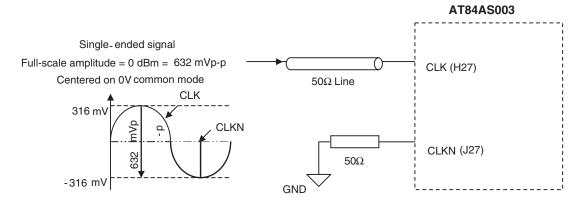

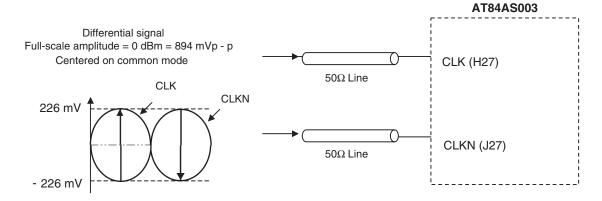

- 100 $\Omega$  Differential or Single-ended 50 $\Omega$  Clock Input

- LVDS Output Compatibility

- Functions:

- ADC Gain Adjust

- Sampling Delay Adjust

- 1:4 Demultiplexed Simultaneous or Staggered Digital Outputs

- Data Ready Output with Asynchronous Reset

- Out-of-range Output Bit (11th Bit)

- Power Consumption: 6.5W

- Power Supplies: –5V, –2.2V, 3.3V and V<sub>PLUSD</sub> Output Power Supply

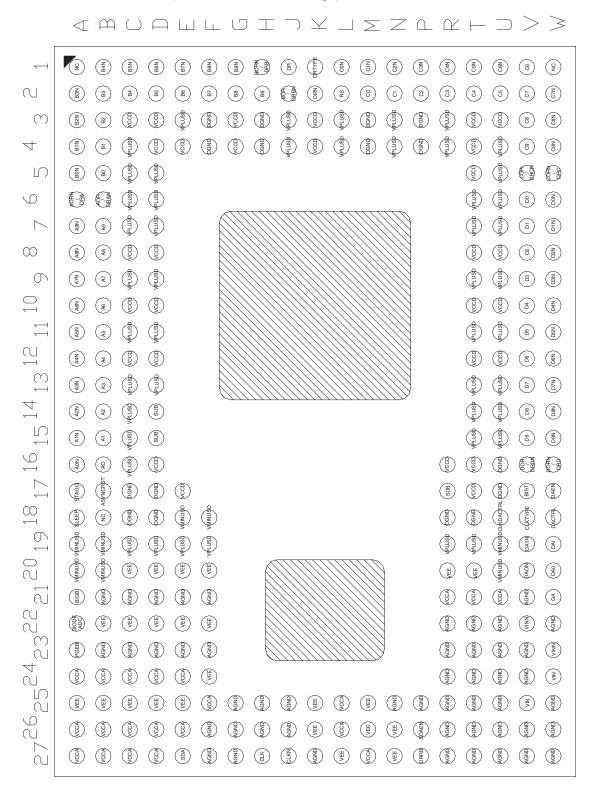

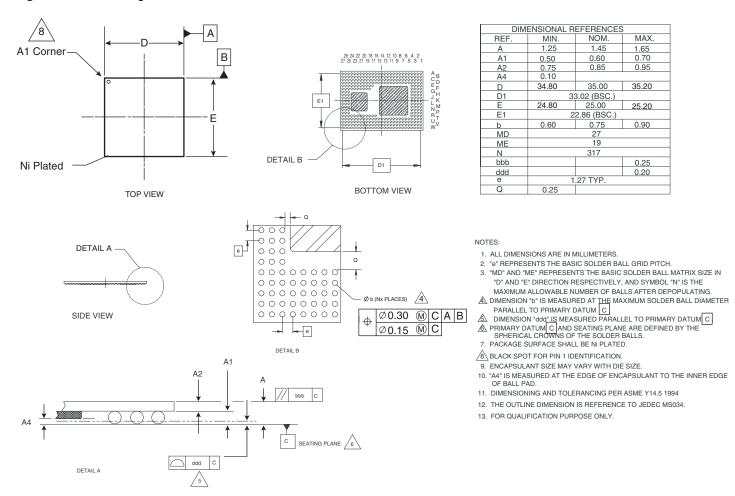

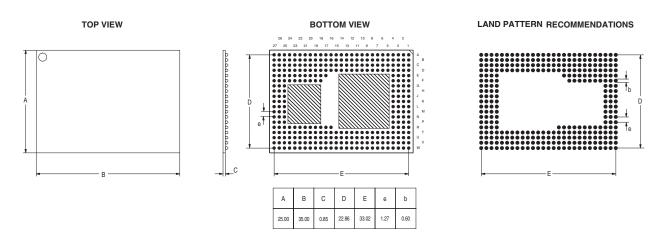

- Package

- Cavity Down EBGA 317 (Enhanced Ball Grid Array)

- 25 x 35 mm Overall Dimensions

#### **Performances**

- 3 GHz Full-power Analog Input Bandwidth

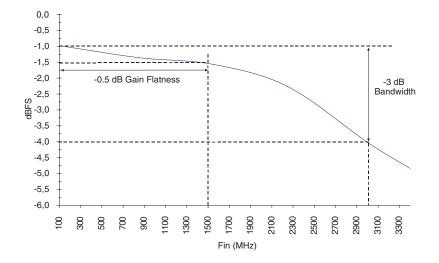

- -0.5 dB Gain Flatness from DC up to 1.5 GHz

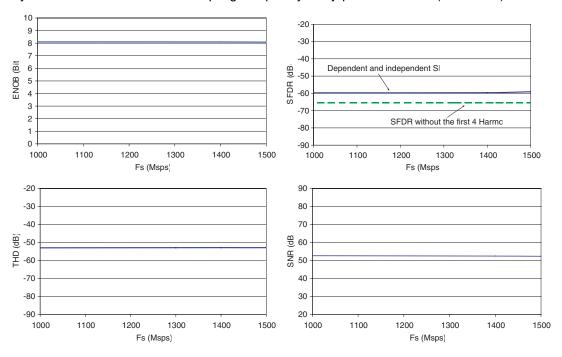

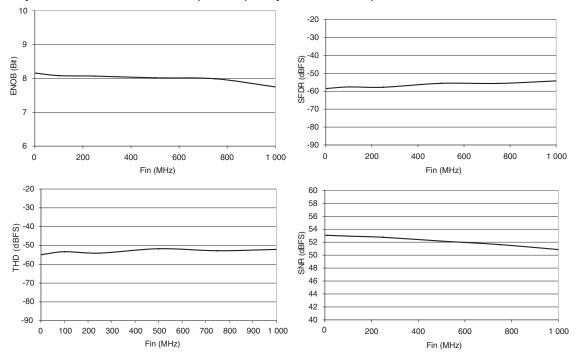

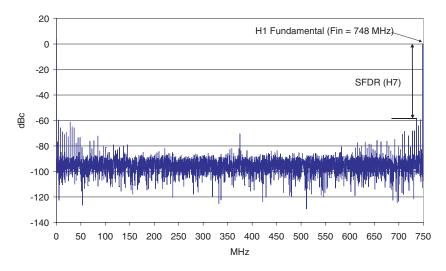

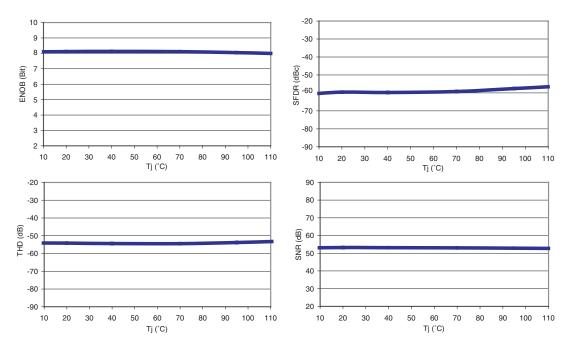

- Single-tone Performance at Fs = 1.5 Gsps, Full First Nyquist Zone

- ENOB = 8.0 Bits,  $F_{IN}$  = 750 MHz

- SNR = 52 dBc, SFDR = 58 dBc,  $F_{IN}$  = 750 MHz

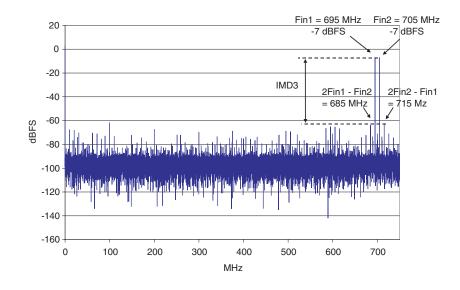

- Dual-tone Performance (IMD3) at Fs = 1.5 Gsps (-7 dBF<sub>S</sub> Each Tone)

- Fin1 = 695 MHz, Fin2 = 705 MHz: IMD3 = -60 dBF<sub>S</sub>

## Screening

- Temperature Range:

- $T_{amb} > 0$ °C;  $T_J < 90$ °C (Commercial *C* Grade)

- T<sub>amb</sub> > -40°C; T<sub>J</sub> < 110°C (Industrial V Grade)

## **Applications**

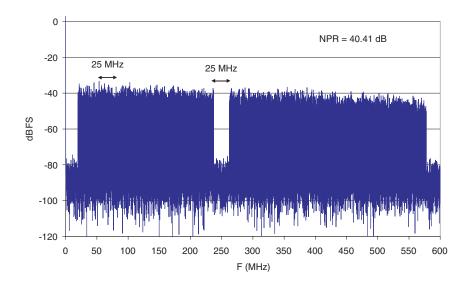

- Direct RF Down Conversion

- Broadband Digital Receivers

- Test Instrumentation

- High Speed Data Acquisition

- High Energy Physics

## 1. Description

The AT84AS003 combines a 10-bit 1.5 Gsps analog-to-digital converter with a 1:4 DMUX, designed for accurate digitization of broadband signals. It features 8.0 effective number of bits (ENOB) and –58 dBc spurious free dynamic range (SFDR) at 1.5 Gsps over the full first Nyquist zone.

The 1:4 demultiplexed digital outputs are LVDS logic compatible, allowing easy interfacing with standard FPGAs or DSPs. The AT84AS003 operates at up to 1.5 Gsps. The AT84AS003 comes in a  $25 \times 35$  mm EBGA 317 package. This package has the same TCE as FR4 boards, offering excellent reliability when submitted to large thermal shocks.

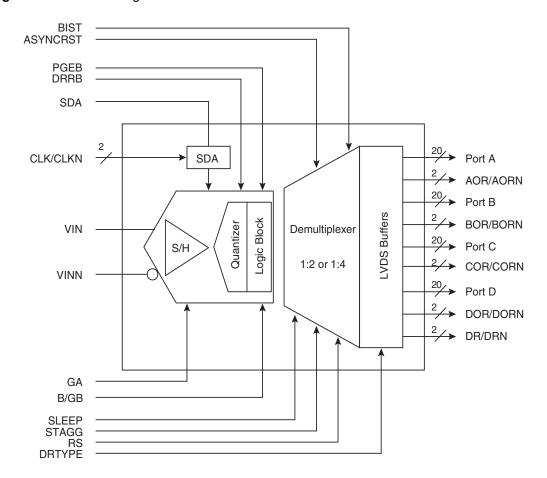

## 2. Block Diagram

Figure 2-1. Block Diagram

## 3. Functional Description

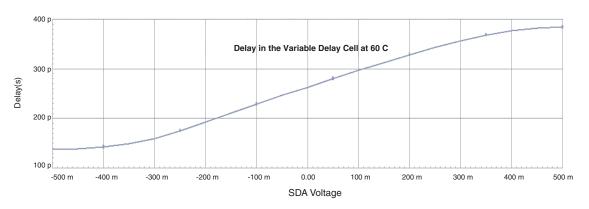

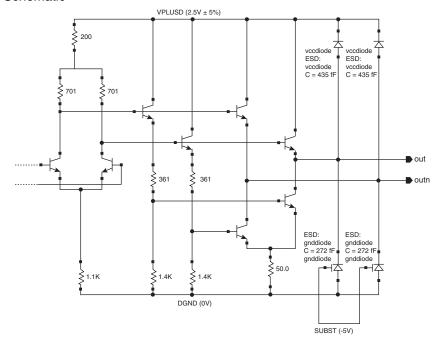

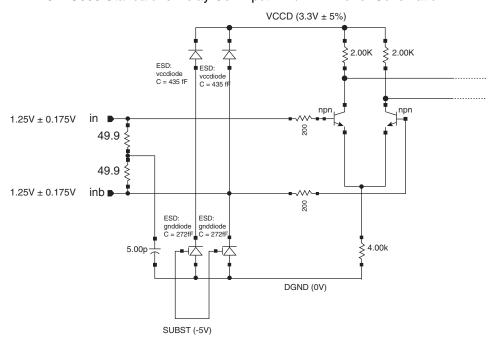

The AT84AS003 is a 10-bit 1.5 Gsps ADC combined with a 1:4 demultiplexer (DMUX) allowing to lower the 11 bit output Data stream (10-bit data and one Out of Range bit) by a selectable factor of 4 or 2. The ADC works in fully differential mode from analog input up to digital outputs.

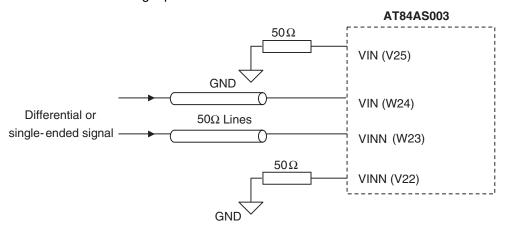

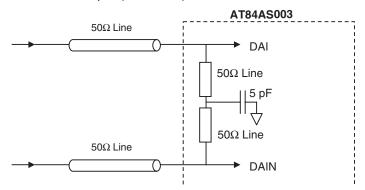

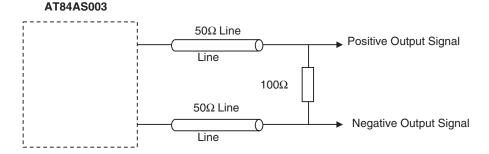

The ADC should be  $50\Omega$  reverse terminated, as close as possible to the EBGA package input pin (1 mm maximum). The ADC clock input is on-chip  $100\Omega$  differentially terminated. The output clock and the output data are LVDS logic compatible, and should be  $100\Omega$  differentially terminated.

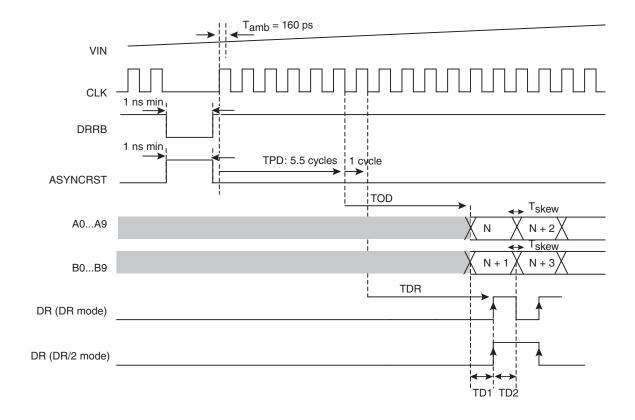

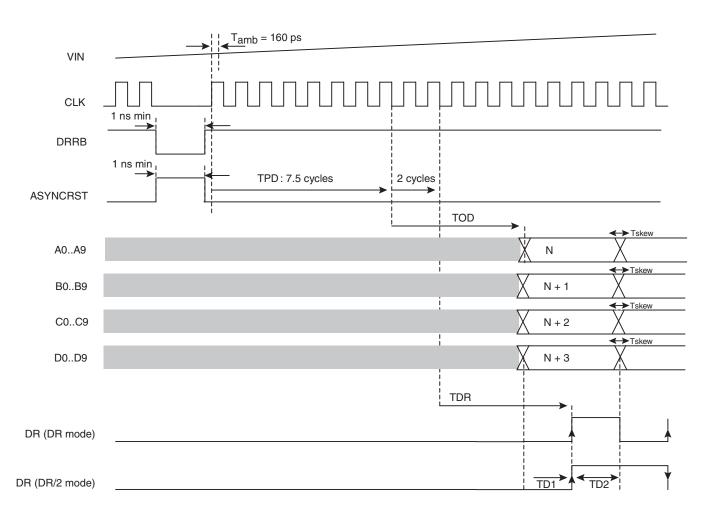

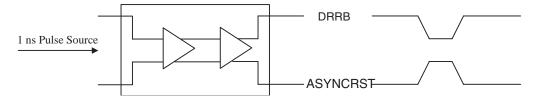

The AT84AS003 ADC features two asynchronous resets:

- DRRB, which ensures that the first digitized data corresponds to the first acquisition.

- ASYNCRST, which ensures that the first digitized data will be output on port A of the DMUX.

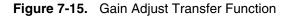

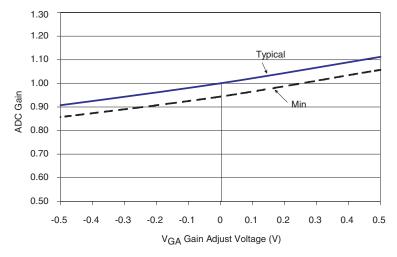

The ADC gain can be tuned in to unity gain by the means of the GA analog control input. A Sampling Delay Adjust function (SDA analog control input, activated via the SDAEN signal) may be used to fine-tune the ADC aperture delay by  $\pm$  120 ps around its center value. The SDA function may be of interest for interleaving multiple ADCs. The control pin B/GB is provided to select either a Binary or Gray data output format.

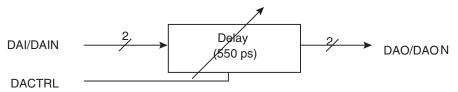

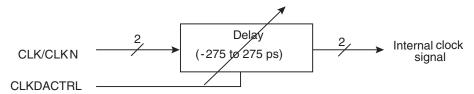

A tunable delay cell (controlled via CLKDACTRL) is integrated between the ADC and the DMUX on the clock path to fine tune the data vs. clock alignment at the interface between the ADC and the DMUX. This delay can be tuned from –275 to 275 ps around default center value, featuring a 550 ps typical delay tuning range. An extra standalone delay cell is also provided, (controlled via DACTRL analog control input and activated via DAEN). The tuning range is typically 550 ps.

A pattern generator (PGEB) is integrated in the ADC part for debug or acquisition setup. Similarly, a built-in self test (BIST) is provided for quick debug of the DMUX part. The output demultiplexing 1:4 or 1:2 ratio can be selected by the means of RS digital control input.

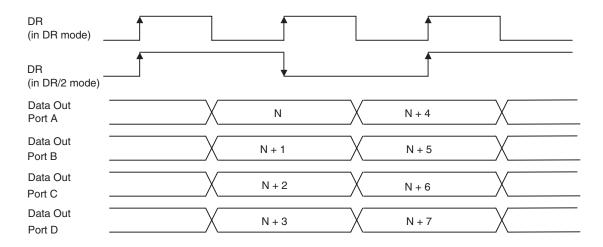

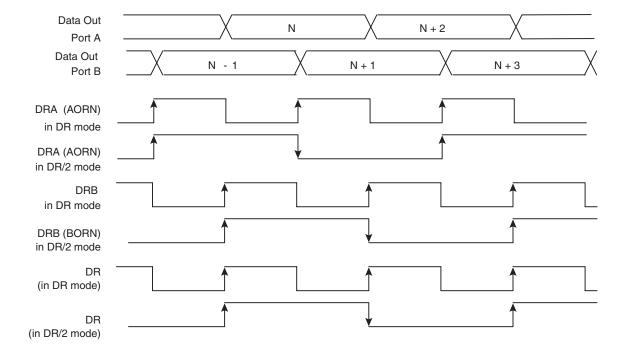

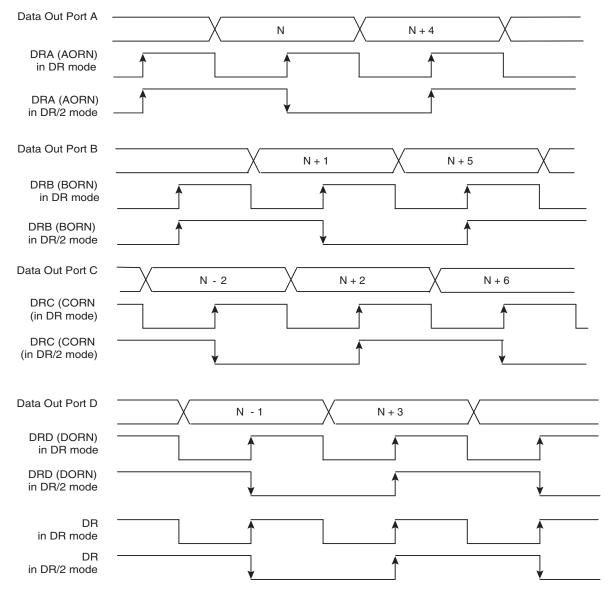

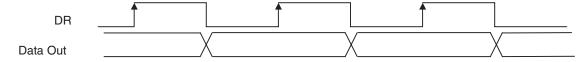

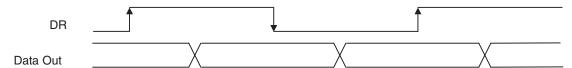

Two modes for the output clock (via DRTYPE) can be selected:

- DR mode: only the output clock rising edge is active, the output clock rate is the same as the output data rate

- DR/2 mode: both the output clock rising and falling edges are active, the output clock rate is half the output data rate

The data outputs are available at the output of the AT84AS003 in two different modes:

- Staggered: even and odd bits come out with half a data period delay

- Simultaneous: even and odd bits come out at the same time

A power reduction mode (SLEEP control input) is provided to reduce the DMUX power consumption.

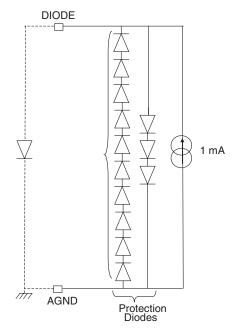

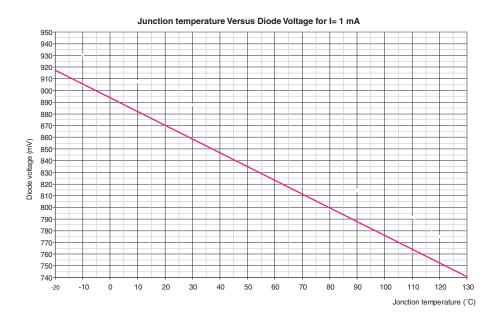

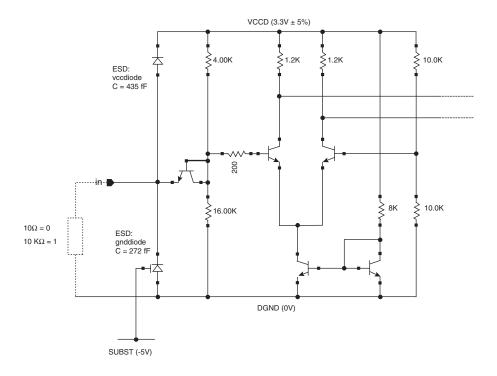

The ADC junction temperature monitoring is made possible through the DIODE input by sensing the voltage drop across 1 diode implemented on the ADC close to chip hot point.

The AT84AS003 is delivered in an Enhanced Ball Grid Array (EBGA), very suitable for applications subjected to large thermal variations (thanks to its TCE which is similar to FR4 material TCE).

Table 3-1.

Functions Description

| Name                  | Function                                                                    |                              |                                                                                       |  |  |

|-----------------------|-----------------------------------------------------------------------------|------------------------------|---------------------------------------------------------------------------------------|--|--|

| V <sub>CCA</sub>      | Analog 3.3V power supply                                                    |                              |                                                                                       |  |  |

| V <sub>CCD</sub>      | Digital 3.3 V power supply                                                  | VC<br>3.0                    | CA VEEVMINUSD VCCDVPLUSD<br>3V -5V -2.2V 3.3V 2.5V                                    |  |  |

| V <sub>EE</sub>       | Analog –5V power supply                                                     | VIN, VINN                    | 20 [A0A9]<br>  1 [A0NA9N]<br>  2 AOR/DRAN,                                            |  |  |

| V <sub>PLUSD</sub>    | Output 2.5 V power supply                                                   | CLK, CLKN <sup>2</sup> →     | AORN/DRA                                                                              |  |  |

| V <sub>MINUSD</sub>   | Output –2.2V power supply                                                   | DRRB→<br>ASYNCRST→<br>SDAEN→ | 20 [B0B9]<br>  B0NB9N]<br>  B0R/DRBN,<br>  BORN/DRB                                   |  |  |

| AGND                  | Analog ground                                                               | SDA → GA PŒB →               | AT84AS003   20   [C0C9]   (C0NC9N)                                                    |  |  |

| DGND                  | Digital ground                                                              | B/GB → DACTRL, CLKDACTR      | CORN/DRC                                                                              |  |  |

| CLK, CLKN             | Input clock signals                                                         | DAI, DAIN SLEEP              | 20 [D0D9]<br>[D0ND9N]<br>2 DOR/DRDN,<br>DORN/DRD                                      |  |  |

| VIN, VINN             | Analog input data                                                           | STAGG→<br>CLKTYPE→<br>RS →   | 2 DR, DRN                                                                             |  |  |

| DRRB                  | ADC reset                                                                   | DAEN → BIST → DRTYPE→        | DAO, DAON  → DIODE ADC                                                                |  |  |

| ASYNCRST              | DMUX asynchronous reset                                                     | Bitti E                      |                                                                                       |  |  |

| DR/DRN                | Output clock signals                                                        |                              | AGND DGND                                                                             |  |  |

| A0A9<br>A0NA9N        | Output data port A                                                          |                              |                                                                                       |  |  |

| AOR/DRAN,<br>AORN/DRA | Out-of-range bit port A or output clock in staggered mode for port A        | Name                         | Function                                                                              |  |  |

| B0B9<br>B0NB9N        | Output data port B                                                          | DAI, DAIN                    | Input signals for standalone delay cell                                               |  |  |

| BOR/DRBN,<br>BORN/DRB | Out-of-range bit port B or output clock in staggered mode for port B        | DAO, DAON                    | Output signals for standalone delay cell                                              |  |  |

| DOMINOTES             | in olaggerea meas is: port 2                                                | GA                           | ADC gain adjust                                                                       |  |  |

| C0C9                  | Output data port C                                                          | SDAEN                        | ADC SDA enable                                                                        |  |  |

| C0NC9N                | Culput data port o                                                          | SDA                          | ADC sampling delay adjust                                                             |  |  |

| COR/DRCN,<br>CORN/DRC | Out-of-range output bit port C or Output clock in staggered mode for Port C | PGEB                         | ADC pattern generator                                                                 |  |  |

| D0D9                  | Output data part D                                                          | B/GB                         | Binary or gray output code selection                                                  |  |  |

| D0ND9N                | Output data port D                                                          | SLEEP                        | Sleep mode selection signal                                                           |  |  |

| DOR/DRDN,<br>DORN/DRD | Out-of-range bit port D or output clock in staggered mode for port D        | STAGG                        | Staggered mode selection for Data outputs                                             |  |  |

| RS                    | DMUX ratio selection signal                                                 | CLKTYPE                      | Input clock type selection signal (to be connected to $V_{\rm CCD}$ or left floating) |  |  |

| CLKDACTRL             | Control signal for clock delay cell                                         | DRTYPE                       | Output clock type selection signal                                                    |  |  |

| DACTRL                | Control signal for standalone delay cell                                    | BIST                         | Built-in Self Test                                                                    |  |  |

| DAEN                  | Enable signal for standalone delay cell                                     | DIODE ADC                    | Diode for die junction temperature monitoring (ADC)                                   |  |  |

## 4. Specifications

## 4.1 Absolute Maximum Ratings

Table 4-1.

Absolute Maximum Ratings

| Parameter                                                             | Symbol                                           | Value                     | Unit |

|-----------------------------------------------------------------------|--------------------------------------------------|---------------------------|------|

| Analog positive supply voltage                                        | V <sub>CCA</sub>                                 | GND to 6                  | V    |

| Digital positive supply voltage                                       | V <sub>CCD</sub>                                 | GND to 3.6                | V    |

| Analog negative supply voltage                                        | $V_{EE}$                                         | GND to -5.5               | V    |

| Digital positive supply voltage                                       | $V_{PLUSD}$                                      | GND to 3                  | V    |

| Digital negative supply voltage                                       | V <sub>MINUSD</sub>                              | GND to -3                 | V    |

| Maximum difference between V <sub>PLUSD</sub> and V <sub>MINUSD</sub> | V <sub>PLUSD</sub> - V <sub>MINUSD</sub>         | 5                         | V    |

| Analog input voltages                                                 | V <sub>IN</sub> or V <sub>INN</sub>              | -1.5 to 1.5               | V    |

|                                                                       | V <sub>IN</sub> - V <sub>INN</sub>               | -1.5 to 1.5               | V    |

| Clock input voltage                                                   | V <sub>CLK</sub> or V <sub>CLKN</sub>            | –1 to 1                   | V    |

| Maximum difference between $V_{\text{CLK}}$ and $V_{\text{CLKN}}$     | V <sub>CLK</sub> - V <sub>CLKN</sub>             | -1 to 1                   | V    |

| Control input voltage                                                 | GA, SDA                                          | -1 to 0.8                 | V    |

| Digital input voltage                                                 | SDAEN, B/GB, PGEB, DECB                          | -5 to 0.8                 | V    |

| ADC reset voltage                                                     | DRRB                                             | $-0.3$ to $V_{CCA} + 0.3$ | V    |

| DMUX function input voltage                                           | RS, CLKTYPE, DRTYPE, SLEEP,<br>STAGG, BIST, DAEN | $-0.3$ to $V_{CCD} + 0.3$ | V    |

| DMUX asynchronous reset                                               | ASYNCRST                                         | $-0.3$ to $V_{CCD} + 0.3$ |      |

| DMUX input voltage                                                    | DAI, DAIN                                        | $-0.3$ to $V_{CCD} + 0.3$ | V    |

| DMUX control voltage                                                  | CLKDACTRL, DACTRL                                | $-0.3$ to $V_{CCD} + 0.3$ | V    |

| Maximum input voltage on DIODE                                        | DIODE ADC                                        | 700                       | mV   |

| Maximum input current on DIODE                                        | DIODE ADC                                        | 1                         | mA   |

| Junction temperature                                                  | T <sub>J</sub>                                   | 135                       | °C   |

Notes:

- 1. Absolute maximum ratings are short term limiting values (referenced to GND = 0 V), to be applied individually, while other parameters are within specified operating conditions. Long exposure to maximum ratings may affect device reliability.

- 2. All integrated circuits have to be handled with appropriate care to avoid damage due to ESD. Damage caused by inappropriate handling or storage could range from performance degradation to complete failure.

Table 4-2. Recommended Condition of Use

| Parameter                                    | Symbol                                                                           | Comments                                                                                             | Recommended Value                                                                                                                                                                 | Unit       |

|----------------------------------------------|----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Positive supply voltage                      | V <sub>CCA</sub>                                                                 |                                                                                                      | 3.3                                                                                                                                                                               | V          |

| Positive supply voltage                      | V <sub>CCD</sub>                                                                 |                                                                                                      | 3.3                                                                                                                                                                               | V          |

| Negative supply voltage                      | V <sub>EE</sub>                                                                  |                                                                                                      | -5.0                                                                                                                                                                              | V          |

| Positive negative supply voltage             | V <sub>MINUSD</sub>                                                              |                                                                                                      | - 2.2                                                                                                                                                                             | V          |

| Differential analog input voltage            | V <sub>IN</sub> - V <sub>INN</sub>                                               |                                                                                                      | 500                                                                                                                                                                               | mVpp       |

| Differential clock input level               | Vinclk                                                                           | $50\Omega$ single-ended (V <sub>INN</sub> grounded through $50\Omega$ )                              | ±125<br>500                                                                                                                                                                       | mV<br>mVpp |

| Clock input power level (ground common mode) | P <sub>CLK</sub> P <sub>CLKN</sub>                                               | $50\Omega$ single-ended clock input or $100\Omega \ \text{differential clok} \ \text{(recommended)}$ | 0                                                                                                                                                                                 | dBm        |

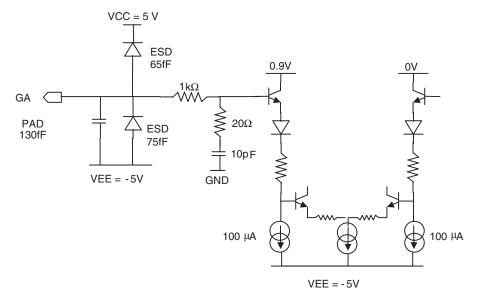

| ADC control input voltage                    | GA, SDA                                                                          |                                                                                                      | -0.5 to 0.5                                                                                                                                                                       | V          |

| ADC functions                                | SDAEN, B/GB, PGEB,<br>DECB                                                       |                                                                                                      | GND or V <sub>EE</sub>                                                                                                                                                            | V          |

| ADC reset                                    | DRRB                                                                             |                                                                                                      | GND to 3.3V                                                                                                                                                                       | V          |

| DMUX standalone delay cell inputs            | DAI, DAIN                                                                        |                                                                                                      | GND to 3.3V                                                                                                                                                                       | V          |

| DMUX control inputs                          | SLEEP, STAGG,<br>ASYNCRST,<br>BIST, RS, DAEN,<br>DRTYPE,<br>CLKDACTRL,<br>DACTRL |                                                                                                      | GND to 3.3V                                                                                                                                                                       | V          |

| Operating temperature range                  | T <sub>C</sub> ; T <sub>J</sub>                                                  | Commercial <i>C</i> grade industrial <i>V</i> grade                                                  | $0^{\circ}\text{C} < \text{T}_{\text{amb}}; \text{T}_{\text{J}} < 90^{\circ}\text{C}$<br>$-40^{\circ}\text{C} < \text{T}_{\text{amb}}, \text{T}_{\text{J}} < 110^{\circ}\text{C}$ | °C         |

| Storage temperature                          | T <sub>stg</sub>                                                                 |                                                                                                      | –55°C to 125                                                                                                                                                                      | °C         |

| Maximum junction temperature                 | T <sub>J</sub>                                                                   |                                                                                                      | 125                                                                                                                                                                               | °C         |

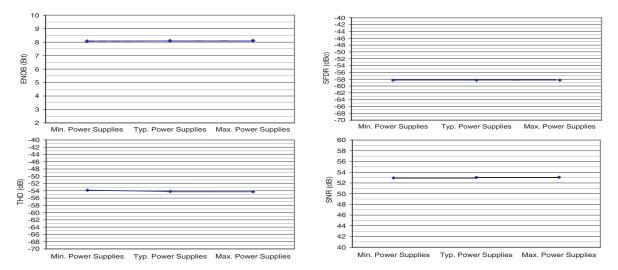

## 4.2 Electrical Operating Characteristics

- $V_{CCA} = V_{CCD} = 3.3V$ ,  $V_{EE} = -5V$ ,  $V_{MINUSD} = -2.2V$

- $V_{INN}$   $V_{INN}$  = 1 dBFS ( single-ended driven with  $V_{INN}$  connected to ground via  $50\Omega$ )

- P<sub>CLK</sub> = 0 dBm (differential driven)

**Table 4-3.** DC Electrical Characteristics at Ambient Temperature and Hot Temperature (T<sub>J</sub> Max)

| Parameter                                                                                                                                                                                                                   | Test<br>Level | Symbol                                                                                        | Min                 | Тур                            | Max                             | Unit                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----------------------------------------------------------------------------------------------|---------------------|--------------------------------|---------------------------------|----------------------|

| Resolution                                                                                                                                                                                                                  |               |                                                                                               |                     | 10                             |                                 | Bit                  |

| Power Requirements                                                                                                                                                                                                          |               |                                                                                               |                     |                                |                                 |                      |

| Positive - analog supply - digital (1) Voltages - digital outputs                                                                                                                                                           | 1             | V <sub>CCA</sub><br>V <sub>CCD</sub><br>V <sub>PLUSD</sub>                                    | 3.15<br>3.15<br>2.4 | 3.3<br>3.3<br>2.5              | 3.45<br>3.45<br>2.6             | V<br>V<br>V          |

| $- analog  V_{CCA} = 3.3V$ $Positive  - digital  V_{CCD} = 3.3V  (1:2  DMUX)$ $Supply  - digital  V_{CCD} = 3.3V  (1:4  DMUX)$ $Current  - output  V_{PLUSD} = 2.5V  (1:2  DMUX)$ $- output  V_{PLUSD} = 2.5V  (1:4  DMUX)$ | 1             | I <sub>VCCA</sub> I <sub>VCCD</sub> I <sub>VCCD</sub> I <sub>VPLUSD</sub> I <sub>VPLUSD</sub> |                     | 80<br>535<br>565<br>440<br>460 | 100<br>590<br>620<br>470<br>490 | mA<br>mA<br>mA<br>mA |

| Negative supply voltage V <sub>EE</sub>                                                                                                                                                                                     | 1             | $V_{EE}$                                                                                      | -5.25               | <b>-</b> 5                     | -4.75                           | V                    |

| Negative supply current                                                                                                                                                                                                     | 1             | I <sub>VEE</sub>                                                                              |                     | 620                            | 660                             | mA                   |

| Negative supply voltage                                                                                                                                                                                                     | 1             | V <sub>MINUSD</sub>                                                                           | -2.3                | -2.2                           | -2.1                            | V                    |

| Negative supply current                                                                                                                                                                                                     | 1             | I <sub>VMINUSD</sub>                                                                          |                     | 190                            | 200                             | mA                   |

| Power Dissipation (1:2 DMUX)                                                                                                                                                                                                | 1             | $P_{D}$                                                                                       |                     | 6.5                            | 7.1                             | W                    |

| Analog Inputs                                                                                                                                                                                                               |               | <u> </u>                                                                                      |                     | 1                              |                                 | <u>"</u>             |

| Full-scale input voltage range Differential mode 0V common mode voltage                                                                                                                                                     | 4             | V <sub>IN</sub><br>V <sub>INN</sub>                                                           | -125<br>-125        |                                | 125<br>125                      | mV<br>mV             |

| Full-scale input voltage range Single-ended input option 0V common mode voltage                                                                                                                                             | 4             | $V_{IN}, V_{INN}$                                                                             | -250                | 0                              | 250                             | mV                   |

| Analog input power level (50Ω single-ended)                                                                                                                                                                                 | 4             | P <sub>IN</sub>                                                                               |                     | -2                             |                                 | dBm                  |

| Analog input capacitance (die)                                                                                                                                                                                              | 4             | C <sub>IN</sub>                                                                               |                     | 0.3                            |                                 | pF                   |

| Input leakage current                                                                                                                                                                                                       | 4             | I <sub>IN</sub>                                                                               |                     | 10                             |                                 | μΑ                   |

| - single-ended Input resistance                                                                                                                                                                                             | 4             | R <sub>IN</sub>                                                                               | 49                  | 50                             | 51                              | Ω                    |

| - differential                                                                                                                                                                                                              |               | R <sub>IN</sub> , <sub>INN</sub>                                                              | 98                  | 100                            | 102                             | Ω                    |

**Table 4-3.** DC Electrical Characteristics at Ambient Temperature and Hot Temperature (T<sub>J</sub> Max) (Continued)

| Parameter                                                                                                               | Test<br>Level | Symbol                                     | Min          | Тур                                | Max          | Unit    |

|-------------------------------------------------------------------------------------------------------------------------|---------------|--------------------------------------------|--------------|------------------------------------|--------------|---------|

| Clock Inputs                                                                                                            |               |                                            |              |                                    | 1            | '       |

| Logic common mode compatibility for clock inputs                                                                        | 4             |                                            | Diffe        | erential ECL to I<br>(AC coupling) | LVDS         |         |

| Clock input common voltage range (V <sub>CLK</sub> or V <sub>CLKN</sub> ) (0V common mode)                              | 4             | V <sub>CM</sub>                            | -1.2         | 0                                  | 0.3          | V       |

| Clock input power level (low-phase noise sinewave input) $50\Omega$ single-ended or $100\Omega$ differential            | 4             | P <sub>CLK</sub>                           | -4           | 0                                  | 4            | dBm     |

| Clock input swing (single ended with CLKN = $50\Omega$ to GND)                                                          | 4             | V <sub>CLK</sub>                           | ± 200        | ± 320                              | ± 500        | mV      |

| Clock input swing (differential voltage) on each clock input                                                            | 4             | V <sub>CLK</sub> , V <sub>CLKN</sub>       | ± 141        | ± 226                              | ± 354        | mV      |

| Clock input capacitance (die)                                                                                           | 4             | C <sub>LK</sub>                            |              | 0.3                                |              | pF      |

| Clock input resistance Single-ended Differential ended                                                                  | 4             | R <sub>CLK</sub><br>R <sub>CLK, CLKN</sub> | 45<br>90     | 50<br>100                          | 55<br>110    | Ω<br>Ω  |

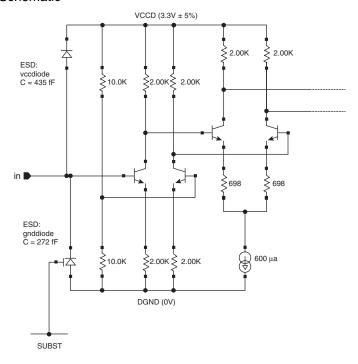

| Digital Data Outputs                                                                                                    |               |                                            |              |                                    |              |         |

| Logic compatibility LVDS                                                                                                |               |                                            |              |                                    |              |         |

| $50\Omega$ transmission lines, $100\Omega$ (2 $\times$ $50\Omega)$ differential termination)<br>Logic low<br>Logic high | 1             | V <sub>OL</sub><br>V <sub>OH</sub>         | -<br>1.25    | 1.075<br>1.425                     | 1.25<br>–    | V       |

| Differential output Common mode                                                                                         |               | $V_{ m ODIFF} \ V_{ m OCM}$                | 250<br>1.125 | 350<br>1.25                        | 500<br>1.375 | mV<br>V |

| Control Function Inputs                                                                                                 |               | • ОСМ                                      | 0            | 0                                  |              |         |

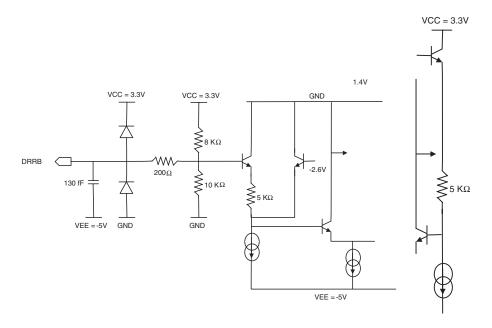

| DRRB and ASYNCRST                                                                                                       |               |                                            |              |                                    |              |         |

| Logic low                                                                                                               | 1             | V <sub>IL</sub>                            | 0            |                                    | 1.0          | V       |

| Logic high                                                                                                              |               | V <sub>IH</sub>                            | 1.6          |                                    | 3.3          | V       |

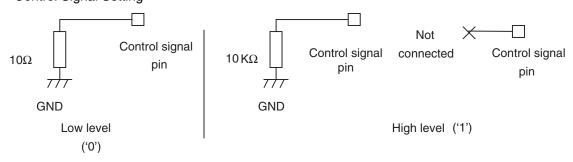

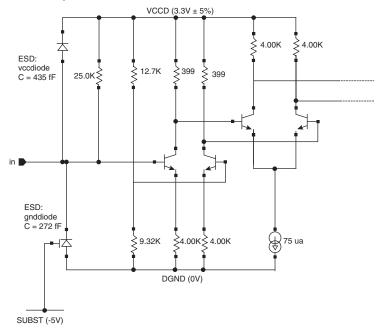

| RS, DRTYPE, SLEEP, STAGG, BIST, DAEN                                                                                    |               |                                            |              |                                    |              |         |

| Logic low                                                                                                               | 4             | V <sub>IL</sub><br>R <sub>IL</sub>         | 0            |                                    | 0.5<br>10    | V<br>Ω  |

| Logic high                                                                                                              |               | V <sub>IH</sub><br>R <sub>IH</sub>         | 2<br>10 K    |                                    | Infinite     | V<br>Ω  |

DC Electrical Characteristics at Ambient Temperature and Hot Temperature (T<sub>J</sub> Max) (Continued) Table 4-3.

| Test<br>Level | Symbol           | Min                  | Тур                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Max                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------|------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               |                  |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

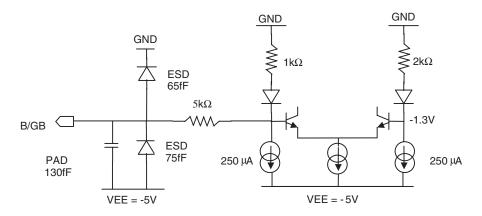

| 1             | $V_{IL}$         |                      | $V_{EE}$                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|               | $V_{IH}$         | -2                   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|               |                  |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1             | $V_{IDIFF}$      | 1                    | 1.25                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|               | $V_{ICM}$        | 100                  | 350                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | mV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1             |                  | -0.5                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1             |                  | $1/3 \times V_{CCD}$ |                                                                                                                                                                                                                                                                                                                                                                                                                                                          | $2/3 \times V_{CCD}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|               |                  |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1             | DNLrms           |                      | 0.2                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | LSB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1             | DNL <sup>-</sup> | -0.8                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | LSB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1             | DNL <sup>+</sup> |                      | 0.8                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | LSB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1             | INL <sup>-</sup> | -4                   | -2                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | LSB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1             | INL+             |                      | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | LSB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1             |                  | 0.95                 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1.05                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 4             |                  |                      | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ppm/°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1             |                  | -10                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | mV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|               | 1 1 1 1 1 1 1 4  | 1                    | Level         Symbol         Min           1         V <sub>IL</sub> V <sub>IH</sub> -2           1         V <sub>IDIFF</sub> V <sub>ICM</sub> 1 00           1         -0.5         1 1/3 × V <sub>CCD</sub> 1         DNLrms         -0.8           1         DNL <sup>-</sup> -0.8           1         DNL <sup>+</sup> -4           1         INL <sup>+</sup> -4           1         INL <sup>+</sup> 0.95           4         -0.95         -0.95 | Level         Symbol         Min         Typ           1         V <sub>IL</sub><br>V <sub>IH</sub> -2         0           1         V <sub>IDIFF</sub><br>V <sub>ICM</sub> 1         1.25<br>100         350           1         -0.5         1         1/3 × V <sub>CCD</sub> 1         DNLrms         0.2         0.2           1         DNL <sup>-</sup> -0.8         0.8           1         INL <sup>-</sup> -4         -2           1         INL <sup>+</sup> 2           1         INL <sup>+</sup> 2           1         0.95         1           4         23 | Level         Symbol         Min         Typ         Max           1         V <sub>IL</sub><br>V <sub>IH</sub> -2         0         0           1         V <sub>IDIFF</sub><br>V <sub>ICM</sub> 1         1.25<br>100         1.6           1         -0.5         0.5         0.5           1         1/3 × V <sub>CCD</sub> 2/3 × V <sub>CCD</sub> 1         DNLrms         0.2         0.3           1         DNL <sup>-</sup> -0.8         1.5           1         INL <sup>-</sup> -4         -2           1         INL <sup>+</sup> 2         4           1         0.95         1         1.05           4         23         35 |

- Notes: 1. For proper operation of BIST mode,  $V_{CCD} = 3.3V$ .

- 2. Histogram testing at Fs = 1.4 Gsps Fin = 695 MHz.

- 3. This range of gain can be set to 1 thanks to the gain adjust function.

**Table 4-4.** AC Electrical Characteristics at Ambient Temperature and Hot Temperature (T<sub>J</sub> Max)

| Parameter                                                                               | Test<br>Level    | Symbol           | Min              | Тур                | Max            | Unit             |  |  |

|-----------------------------------------------------------------------------------------|------------------|------------------|------------------|--------------------|----------------|------------------|--|--|

| AC Analog Inputs                                                                        | AC Analog Inputs |                  |                  |                    |                |                  |  |  |

| Full power input bandwidth (1)                                                          | 4                | FPBW             |                  | 3                  |                | GHz              |  |  |

| Small signal input bandwidth (10% full-scale)                                           | (1) 4            | SSBW             |                  | 3.3                |                | GHz              |  |  |

| Gain flatness (2)                                                                       | 4                | BF               |                  | -0.5               |                | dB               |  |  |

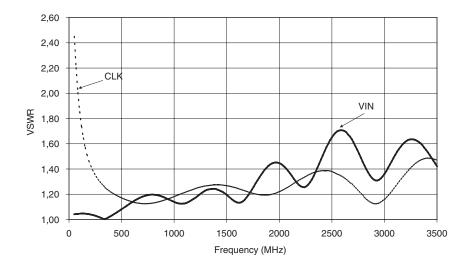

| Input voltage standing wave ration (3)                                                  | 4                | VSWR             |                  | 1.1: 1             | 1.2: 2         |                  |  |  |

| AC Performance: Nominal Condition at Ambie                                              | ent Temperature  | 9                | ı                | ,                  |                |                  |  |  |

| <ul> <li>-1 dBFS single-ended input mode (unless oth<br/>output data format.</li> </ul> | nerwise specifie | ed); 50% clock d | uty cycle; 0 dBm | n differential clo | ck (CLK, CLKN) | ); binary        |  |  |

| Effective Number of Bits                                                                |                  |                  |                  |                    |                |                  |  |  |

| Fs = 1 Gsps Fin = 100 MHz<br>Fs = 1.5 Gsps Fin = 750 MHz                                | 1                | ENOB             | 7.4<br>7.4       | 8.0<br>8.0         |                | Bit              |  |  |

| Signal to Noise Ratio                                                                   |                  |                  |                  |                    |                |                  |  |  |

| Fs = 1 Gsps Fin = 100 MHz<br>Fs = 1.5 Gsps Fin = 750 MHz                                | 1                | SNR              | 50<br>49         | 52<br>52           |                | dBc              |  |  |

| Total Harmonic Distortion                                                               |                  |                  |                  |                    |                |                  |  |  |

| Fs = 1 Gsps Fin = 100 MHz<br>Fs = 1.5 Gsps Fin = 750 MHz                                | 1                | ITHDI            | 46<br>46         | 52<br>52           |                | dBc              |  |  |

| Spurious Free Dynamic Range                                                             |                  |                  |                  |                    |                |                  |  |  |

| Fs = 1 Gsps       Fin = 100 MHz         Fs = 1.5 Gsps       Fin = 750 MHz               | 1                | ISFDRI           | 50<br>50         | 58<br>58           |                | dBc              |  |  |

| Two-tone Third Order Intermodulation Distortion                                         |                  |                  |                  |                    |                |                  |  |  |

| Fs = 1.5 Gsps (-7 dBF each tone)<br>Fin1 = 695 MHz; Fin2 = 705 MHz                      | 4                | IIMD3I           |                  | 60                 |                | dBF <sub>S</sub> |  |  |

Notes: 1. See "Definition of Terms" on page 41.

<sup>2.</sup> From DC to 1.5 GHz.

<sup>3.</sup> Specified from DC up to 2.5 GHz input signal. Input VSWR is measured on a soldered device. It assumes an external  $50\Omega \pm 2\Omega$  controlled impedance line, and a  $50\Omega$  driving source impedance ( $S_{11} \le 30$  dB).

Table 4-5.

Transient and Switching Performances

| Parameter                                                                                                 | Test<br>Level | Symbol             | Min               | Тур                                      | Max | Unit             |

|-----------------------------------------------------------------------------------------------------------|---------------|--------------------|-------------------|------------------------------------------|-----|------------------|

| Transient Performance                                                                                     |               |                    |                   |                                          |     | <u>'</u>         |

| Bit error rate (1)                                                                                        | 4             | BER                | 10 <sup>-11</sup> |                                          |     | Error/<br>sample |

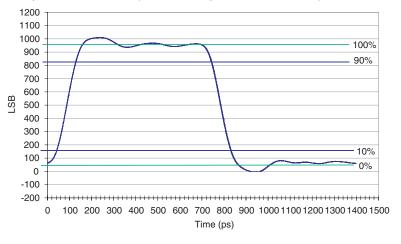

| ADC setting time (V <sub>IN</sub> -V <sub>INN</sub> = 400 mVpp)                                           | 4             | TS                 |                   | 400                                      |     | ps               |

| Overvoltage recovery time                                                                                 | 4             | ORT                |                   |                                          | 500 | ps               |

| ADC step response rise/fall time (10 –90%)                                                                | 4             |                    |                   | 80                                       | 100 | ps               |

| Overshoot                                                                                                 | 5             |                    |                   | 4                                        |     | %                |

| Ringback                                                                                                  | 5             |                    |                   | 2                                        |     | %                |

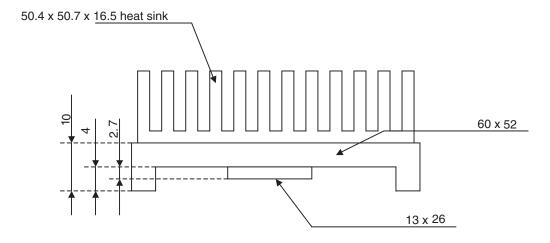

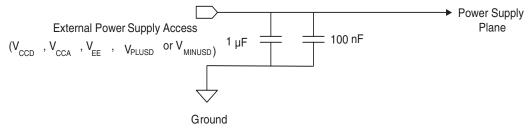

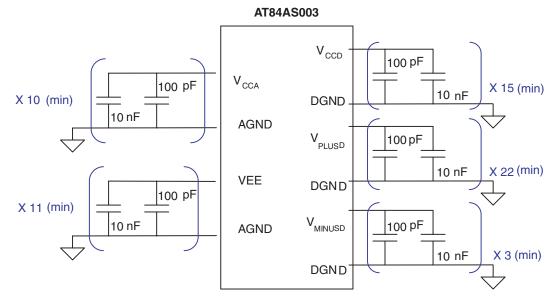

| Switching Performance and Characteristic                                                                  | s             |                    |                   |                                          |     |                  |